# Fine-Grain Distributed Shared Memory on Clusters of Workstations

by

# Ioannis T. Schoinas

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN—MADISON

## **Abstract**

Shared memory, one of the most popular models for programming parallel platforms, is becoming ubiquitous both in low-end workstations and high-end servers. With the advent of low-latency networking hardware, clusters of workstations strive to offer the same processing power as high-end servers for a fraction of the cost. In such environments, shared memory has been limited to page-based systems that control access to shared memory using the memory's page protection to implement shared memory coherence protocols. Unfortunately, false sharing and fragmentation problems force such systems to resort to weak consistency shared memory models that complicate the shared memory programming model.

This thesis studies fine-grain distributed shared memory (FGDSM) systems on networks of workstations to support shared memory and it explores the issues involved in the implementation of FGDSM systems on networks of commodity workstations running commodity operating systems. FGDSM systems rely on fine-grain memory access control to selectively restrict reads and writes to cache-block-sized memory regions. The thesis presents Blizzard, a family of FGDSM systems running on a network of workstations. Blizzard supports the Tempest interface that implements shared memory coherence protocols as user-level libraries. Therefore, application-specific protocols can be developed to eliminate the overhead of the fine-grain access control.

First, this thesis investigates techniques to implement fine-grain access control on commodity workstations. It presents four different techniques that require little or no additional hardware (software checks with executable editing, the memory's controller ECC, a combination of these two techniques, and a custom fine-grain access control accelerator board). Furthermore, the thesis examines the integration of hardware fine-grain techniques within commodity operating systems.

Second, this thesis investigates messaging subsystem design for shared memory coherence protocols. It explores implications of extending Berkeley active messages so that explicit polling is not required and protocols are not limited to request/reply semantics. The thesis explores supporting implicit polling using binary rewriting to insert polls in the application code. In addition, it shows that shared memory coherence protocols, while not pure request/reply protocols, have bounded buffer requirements. Accordingly, it proposes a buffer allocation policy that does not require buffers in a node's local memory in the common case, yet is robust enough to handle arbitrary traffic streams.

Third, this thesis investigates extending FGDSM systems to clusters of multiprocessor workstations. FGDSM systems are especially suited for supporting shared memory on multi-

processor networks, because they transparently extend the fine-grain sharing within the node across the network. The thesis identifies the shared FGDSM resources to which access should be controlled in a multiprocessor environment and proposes techniques to address the synchronization issues for each resource that are based on the frequency of accesses to that resource.

Fourth, this thesis investigates address translation in network interfaces to support zerocopy messaging directly to user data structures. Good messaging performance is important for application-specific protocols that push the limits of the messaging hardware. The thesis evaluates a series of designs with increasingly higher operating system support requirements. It proposes techniques to take advantage of locality in the source or destination virtual memory addresses, yet degrade gracefully when the capacity of the address translation structures is exceeded.

# Acknowledgments

This journey began six and a half years ago when I first arrived in Madison and enrolled as a graduate student in the Computer Sciences Department. I never got used to Madison's long and cold winters, but looking back through the years, I must say that it has been a rewarding experience. I would like to thank all the people that contributed to the successful conclusion of my journey.

I would like to thank my advisor, Mark Hill, for his guidance, support, and encouragement throughout my work. Mark with Jim Larus and David Wood led the Wisconsin Wind Tunnel project and created the intellectual environment that made my work possible. The members of my thesis committee, Mark Hill, David Wood, Marvin Solomon, Pei Cao and Charles Kime have my gratitude for their patience in reading my thesis and for their critical comments in its content and presentation.

I would like to thank all the members of the Wisconsin Wind Tunnel group and the computer architecture community for their comments and debates. Many thanks to Eric Schnarr, Babak Falsafi, Steven Reinhardt, Rob Pfile, Brian Toonen, Chris Lukas, Mark Dionne, Yuanyuan Zhou, and Rich Martin for their contributions in building Blizzard on Wisconsin COW. I would also like to thank Madhu Talluri, Andy Glew, and Steve Scott for their comments on my work. Thanks to Satish Chandra, Trishul Chilimbi, and Alain Kagi for bravely serving as my guinea pigs (i.e., Blizzard users).

I would like to thank the people in the University of Crete for helping me start on the path that lead me to this accomplishment. Yannis Fragiadakis offered me my first computer job. Manolis Katevenis sparked my interest in computer architecture. Stelios Orfanoudakis and Petros Kofakis guided throughout my graduate work in Crete. Finally, I would like to thank my friends in Salonica and Heraclion for sharing with me the pains and pleasures of growing and for encouranging me on my journey to Madison.

I would like to thank the greek community of UW-Madison, and especially Yannis Ioannidis, Thanos Tsiolis and Yiorgos Kalfas for their warm welcoming. Thanks to my old roommates, Markos Zaharioudakis, Gul Gurkan, Yannis Christou, Andreas Moshovos, and Josef Betouras, for their friendship. I should also thank them along with Stefanos Kaxiras, Afroditi Michailidi, Dionisios Pnevmatikatos and Minos Garofalakis for our coffee breaks. I wish also to thank Bill and Katherine Parks for their support and love ever since the first time we met.

My journey would not have been possible without the love that my family gave to me throughout my life. I would like to thank my father, Theofilos Schoinas, and my mother, Eirini Diakaki-Schoina, for patiently raising me to adulthood and for providing me with a solid education. I cannot ever repay my mother for her contribution in building my character and for

showing me the true meaning of love, devotion, and sacrifice. I cannot thank my brother, Michael Schoinas, enough for taking care of things while I was studying abroad. Finally, I would like to thank the love of my heart, Leah Parks, for her love, support and friendship. If it wasn't for you Leah, Madison's winters would have been colder and lonelier. I still can't believe that I met someone like you in Madison, Wisconsin.

# **Contents**

| Abstract     | i                                                             |

|--------------|---------------------------------------------------------------|

| Acknowled    | gmentsii                                                      |

| Contents     | v                                                             |

| List of Figu | resx                                                          |

| List of Tabl | esxi                                                          |

| Chapter 1.   | Introduction                                                  |

| 1.1 Fin      | e-Grain Distributed Memory In Perspective                     |

| 1.2 Sys      | stem Overview5                                                |

| 1.2.1        | Wisconsin Cluster Of Workstations                             |

| 1.2.2        | Blizzard and FGDSM Resources                                  |

| 1.2.3        | Tempest                                                       |

| 1.2.4        | Stache                                                        |

| 1.3 Th       | esis Overview                                                 |

| Chapter 2.   | Fine Grain Access Control14                                   |

| 2.1 Fin      | ne Grain Access Control Design Space                          |

| 2.1.1        | Access Check                                                  |

| 2.1.2        | Protocol Action                                               |

| 2.2 Fin      | e-Grain Access Control Abstraction                            |

| 2.3 Bli      | zzard Fine Grain Access Control Implementations               |

| 2.3.1        | Blizzard/S: Binary Rewriting                                  |

| 2.3.2        | Blizzard/E: Memory Error Correction Code & Page Protection 23 |

| 2.3.3    | Blizzard/ES: Memory Error Correction Code & Binary Rewriting . | 27 |

|----------|----------------------------------------------------------------|----|

| 2.3.4    | Blizzard/T: Custom Accelerator                                 | 27 |

| 2.4 Ker  | nel Support For Fine Grain Access Control                      | 30 |

| 2.4.1    | Design Methodology                                             | 30 |

| 2.4.2    | Solaris Basics                                                 | 32 |

| 2.4.3    | Blizzard Segment Driver                                        | 34 |

| 2.4.4    | Pageout Intercepts                                             | 35 |

| 2.4.5    | Hat Intercepts                                                 | 35 |

| 2.4.6    | Low Level Trap Handler                                         | 37 |

| 2.4.7    | High Level Trap Handler                                        | 40 |

| 2.4.8    | Hardware Device Drivers (ECCMemD, VortexD)                     | 41 |

| 2.5 Fine | e-Grain Access Control Performance                             | 43 |

| 2.5.1    | Access Check Overhead                                          | 43 |

| 2.5.2    | Access Change Overhead                                         | 45 |

| 2.5.3    | Access Fault Overhead                                          | 46 |

| 2.5.4    | Protocol Interactions                                          | 47 |

| 2.6 Con  | clusions                                                       | 49 |

|          |                                                                | =. |

|          | Messaging Subsystem Design                                     |    |

|          | npest Messaging Subsystem                                      |    |

| 3.1.1    | Fine-grain communication: Active Messages                      |    |

|          | Bulk-data transfers: Channels                                  |    |

|          | fer Allocation And Active Messages                             |    |

| 3.2.1    | A Methodology For Analyzing Buffer Requirements                |    |

| 3.2.2    | Parallel Programs and Buffer Requirements                      |    |

| 3.3 Buf  | fer Allocation Policies                                        |    |

| 3.3.1    | Pure Request/Reply                                             |    |

| 3.3.2    | Return-to-Sender                                               |    |

| 3.3.3    | Sender-Overflow                                                | 65 |

| 3.3.4    | Receiver-Overflow                                              | 66 |

|                      |        | vii                                                      |

|----------------------|--------|----------------------------------------------------------|

|                      | 3.3.5  | Sender-Overflow Revisited                                |

| 3.4                  | COV    | V Communication Infrastructure69                         |

| 3.5                  | Tran   | sparent Message Notification                             |

|                      | 3.5.1  | Interrupt Message Notification Alternatives              |

|                      | 3.5.2  | Polling Message Notification Alternatives                |

| 3.6                  | Blizz  | zard Implementation Details                              |

|                      | 3.6.1  | Message Injection                                        |

|                      | 3.6.2  | Handler Dispatch                                         |

| 3.7                  | Perf   | ormance                                                  |

|                      | 3.7.1  | Small Message Latency                                    |

|                      | 3.7.2  | Large Message Latency                                    |

|                      | 3.7.3  | Large Message Throughput                                 |

| 3.8                  | S Cond | clusions                                                 |

| Chant                | or 1   | Blizzard Performance86                                   |

| <b>دانمور</b><br>4.1 |        |                                                          |

|                      |        | Level Performance Characteristics                        |

| 4.2                  |        | llel Applications                                        |

| 4.3                  |        | lication Performance                                     |

|                      | 4.3.1  | Transparent Shared Memory Performance                    |

|                      | 4.3.2  | Application-Specific Protocol Performance                |

|                      |        | Protocol and Message Statistics                          |

|                      | 4.3.4  | Evaluating Fine-grain Access Control Alternatives        |

| 4.4                  | Blizz  | zard Evaluation                                          |

|                      | 4.4.1  | Remote Memory References and Application Performance 102 |

|                      | 4.4.2  | Blizzard vs. Other Approaches                            |

| 4.5                  | Cone   | clusions                                                 |

| Chapt                | er 5.  | Blizzard On Multiprocessor Nodes                         |

| 5.1                  | FGD    | OSM Resources & SMP Nodes                                |

| 5.2                  | Bliza  | zard Implementation Overview                             |

| V | 11 | 1 |

|---|----|---|

| • | •  |   |

|   |    |   |

| 5.3    | Fine  | -Grain Tags                                          |

|--------|-------|------------------------------------------------------|

| 5.4    | Fact  | ors Affecting SMP-Node Performance                   |

| 5.5    | SMI   | P Nodes and Protocol Traffic                         |

| 5.6    | Perf  | ormance Evaluation                                   |

|        | 5.6.1 | Base System Performance                              |

|        | 5.6.2 | SMP-Correctness Overhead in SMP Nodes                |

|        | 5.6.3 | Performance Impact of SMP Nodes                      |

| 5.7    | Rela  | ted Work                                             |

| 5.8    | Con   | clusions                                             |

|        |       |                                                      |

| -      |       | Address Translation Mechanisms in Network Interfaces |

| 6.1    |       | imal Messaging                                       |

| 6.2    |       | ress Translation Properties For Minimal Messaging    |

| 6.3    | Add   | ress Translation Implementation Alternatives         |

|        | 6.3.1 | NI Lookup NI Miss Service                            |

|        | 6.3.2 | NI Lookup CPU Miss Service                           |

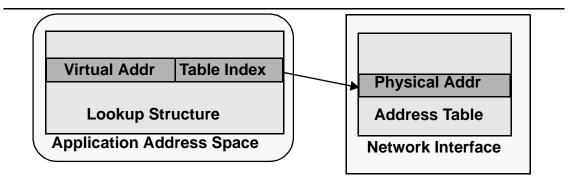

|        | 6.3.3 | CPU Lookup CPU Miss Service                          |

|        | 6.3.4 | CPU Miss Service Optimizations                       |

| 6.4    | FGE   | SM Systems & Minimal Messaging                       |

| 6.5    | Eval  | uation                                               |

|        | 6.5.1 | Simulation Framework                                 |

|        | 6.5.2 | Simulation Results                                   |

|        | 6.5.3 | Blizzard Framework                                   |

|        | 6.5.4 | Blizzard Results                                     |

| 6.6    | Rela  | ted Work                                             |

| 6.7    | Con   | clusions                                             |

| Chapte | er 7. | Conclusions                                          |

| 7.1    | Thes  | sis Summary                                          |

| 7.2    | Imp   | ications                                             |

| 1 | Y |  |

|---|---|--|

|                      | ix                                               |

|----------------------|--------------------------------------------------|

| 7.3 Future Direction | s168                                             |

| 7.3.1 Fault Toler    | rance                                            |

| 7.3.2 COW Virtu      | nalization                                       |

| Appendix A. Blizzard | Implementation                                   |

| A.1 Wisconsin Clus   | ter Of Workstations (COW)                        |

| A.2 Distributed Job  | Manager (DJM)                                    |

| A.3 Tempest Interfa  | ce                                               |

| A.4 Blizzard Implen  | nentation                                        |

| A.4.1 Blizzard C     | Overview                                         |

| A.4.2 Blizzard P     | rotocol libraries                                |

| A.4.3 Virtual Me     | emory Management & Fine-Grain Access Control 181 |

| A.4.4 Fine-Grain     | Messaging                                        |

| A.4.5 Bulk data      | transfer                                         |

| A.4.6 Thread ma      | nagement & Protocol Dispatching                  |

| A.4.7 Compiling      | Blizzard Applications & Libraries                |

| A.4.8 Running B      | Slizzard Applications                            |

| References           | 192                                              |

# **List of Figures**

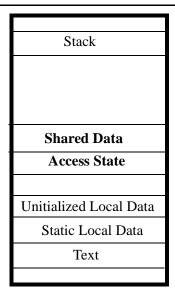

| Figure 1-1.  | Process address space and initialization of shared pages           | 8 |

|--------------|--------------------------------------------------------------------|---|

| Figure 1-2.  | Resources in a software FGDSM system                               | 9 |

| Figure 2-1.  | Software Access Control Instruction Sequences                      | 4 |

| Figure 2-2.  | Process address space with Blizzard/S2                             | 5 |

| Figure 2-3.  | Process address space with Blizzard/E                              | 6 |

| Figure 2-4.  | Process address space with Blizzard/ES                             | 8 |

| Figure 2-5.  | Process address space with Blizzard/T2                             | 9 |

| Figure 2-6.  | Kernel Module Structure                                            | 2 |

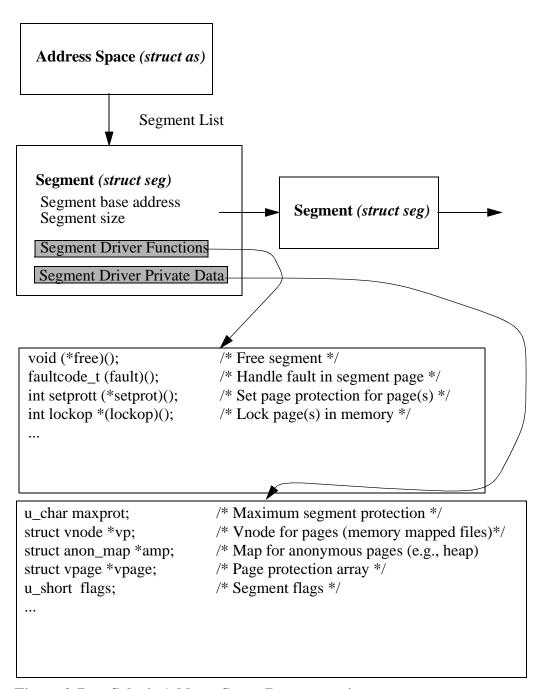

| Figure 2-7.  | Solaris Address Space Representation                               | 3 |

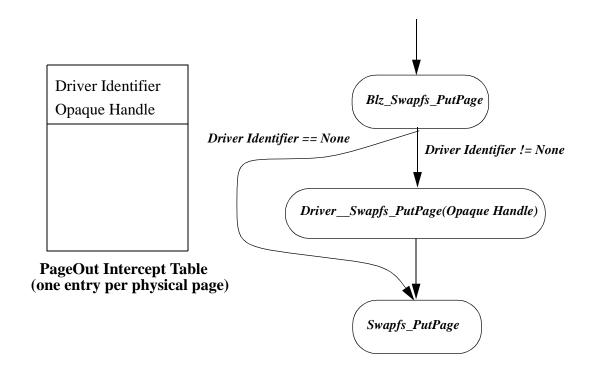

| Figure 2-8.  | PageOut Intercept                                                  | 6 |

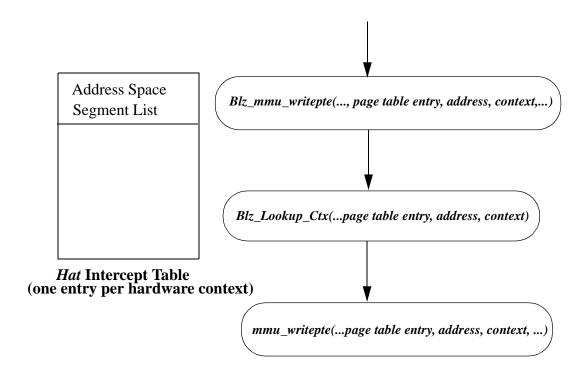

| Figure 2-9.  | HAT Intercept                                                      | 7 |

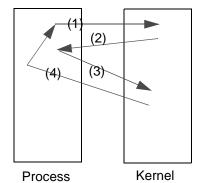

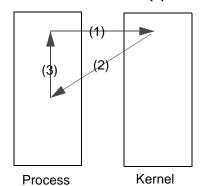

| Figure 2-10. | Signal vs. Fast Trap Interface                                     | 9 |

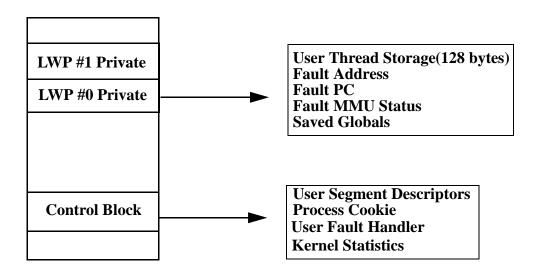

| Figure 2-11. | Fast Trap User/Kernel Interface                                    | 1 |

| Figure 3-1.  | Tempest Active Message Primitives                                  | 4 |

| Figure 3-2.  | Tempest Bulk Data Transfer Primitives                              | 6 |

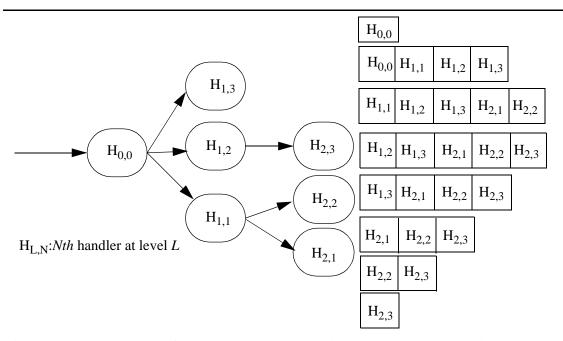

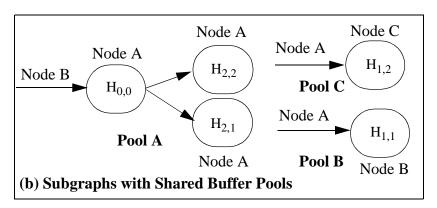

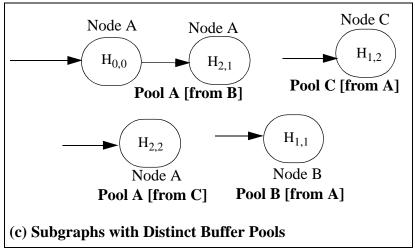

| Figure 3-3.  | Example of a message handler activation graph with a single node 6 | 0 |

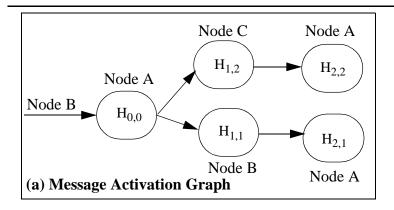

| Figure 3-4.  | Partitioning a message activation graph with three nodes           | 1 |

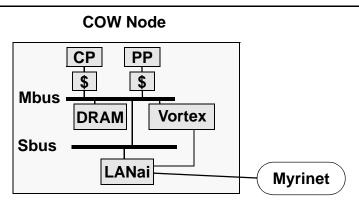

| Figure 3-5.  | COW Hardware Organization                                          | 9 |

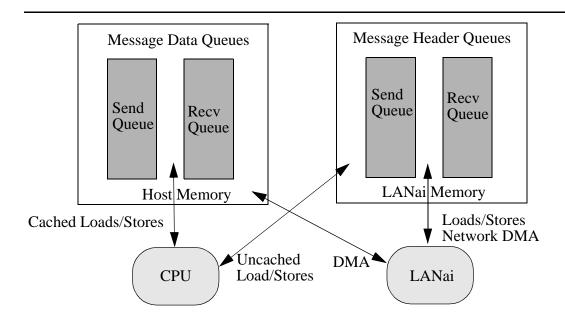

| Figure 3-6.  | Low Level Data Format                                              | 0 |

| Figure 3-7.  | Message Queues And Accesses                                        | 1 |

| Figure 3-8.  | Poll Code Sequences                                                | 4 |

| Figure 3-9.  | Tempest extensions for Blizzard/SYSV                               | 7 |

| Figure 3-10. | Message Injection                                                  | 7 |

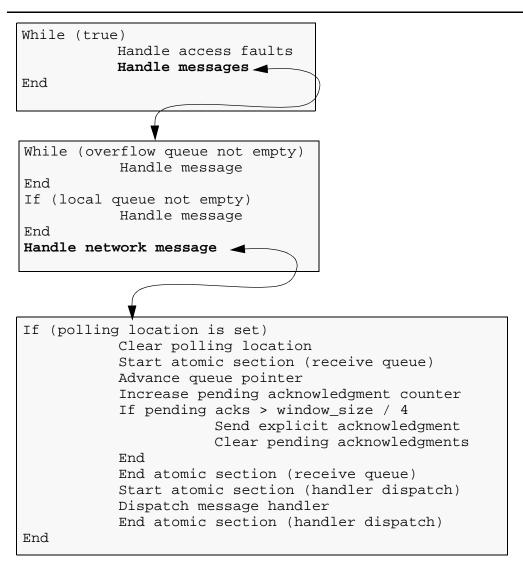

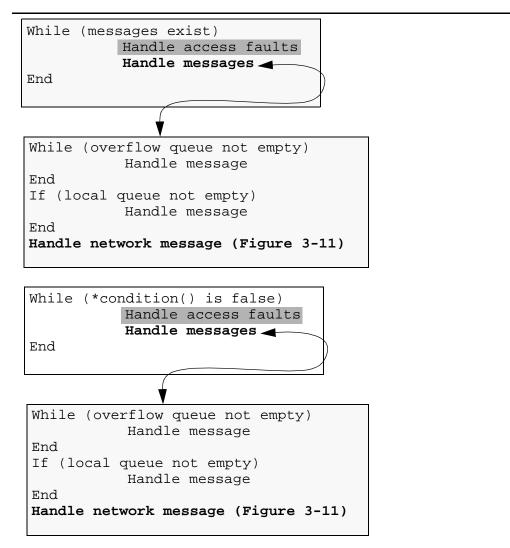

| Figure 3-11. | Message dispatch with a network coprocessor                        | 9 |

| Figure 3-12. | Message dispatch with executable editing8                          | 0 |

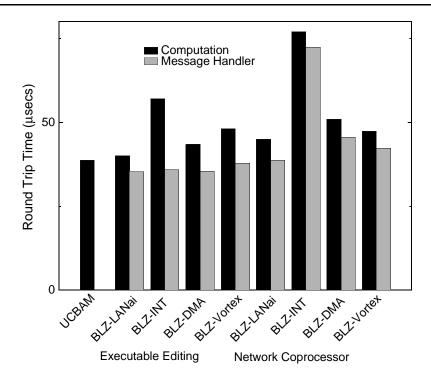

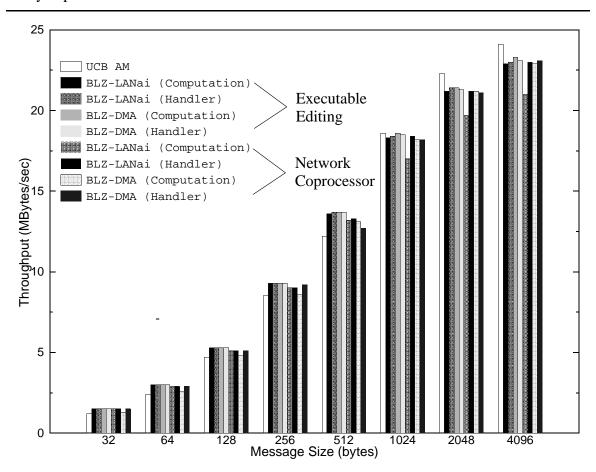

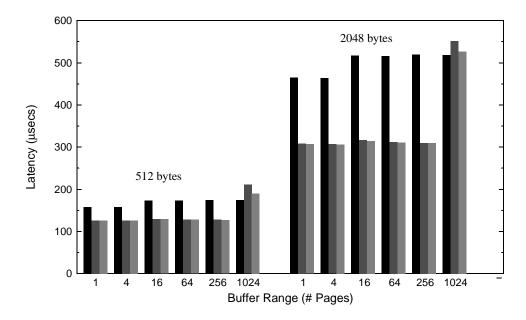

| Figure 3-13. | Small Message Latency                                        |

|--------------|--------------------------------------------------------------|

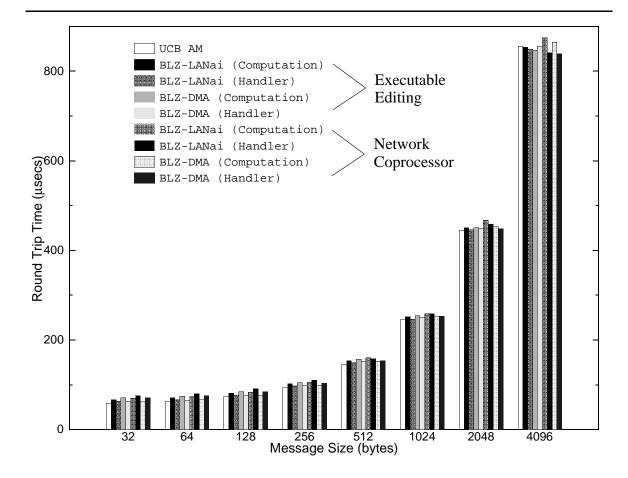

| Figure 3-14. | Large Message Latency                                        |

| Figure 3-15. | Large Message Bandwidth                                      |

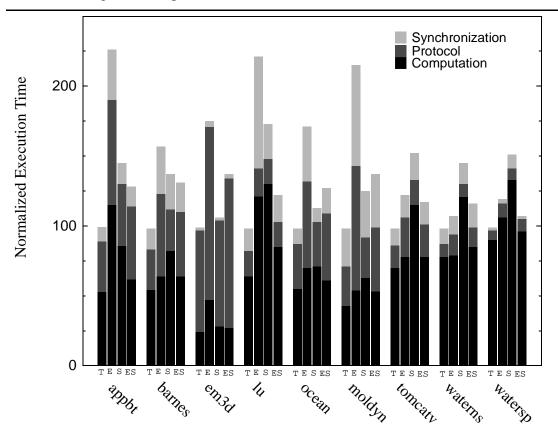

| Figure 4-1.  | Transparent shared memory application performance (stache)96 |

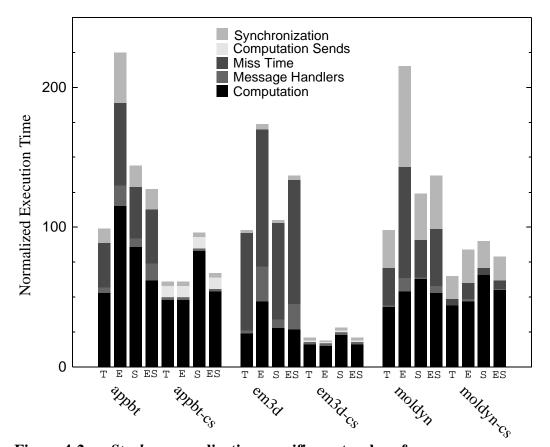

| Figure 4-2.  | Stache vs. application-specific protocol performance         |

| Figure 5-1.  | Anatomy of a software FGDSM node:                            |

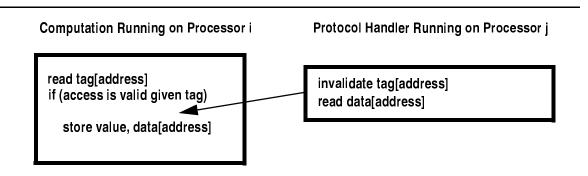

| Figure 5-2.  | Example of race conditions in tag accesses                   |

| Figure 5-3.  | Software handshake in Blizzard/S                             |

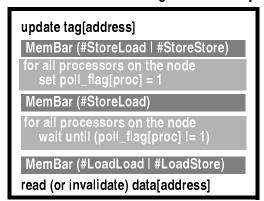

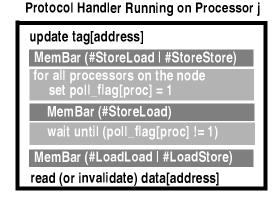

| Figure 5-4.  | Software handshake in Blizzard/SB                            |

| Figure 5-5.  | Software handshake with epochs                               |

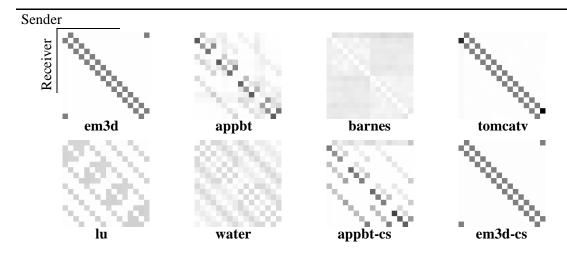

| Figure 5-6.  | Application message traffic (sharing) patterns               |

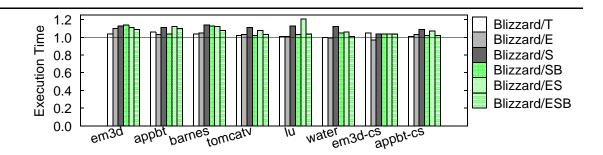

| Figure 5-7.  | SMP-correctness overhead in Blizzard                         |

| Figure 5-8.  | Performance of SMP Nodes in Blizzard                         |

| Figure 6-1.  | Minimal messaging event sequence                             |

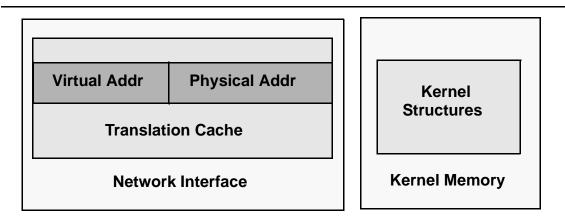

| Figure 6-2.  | NI Lookup NI Miss Service                                    |

| Figure 6-3.  | NI Lookup CPU Miss Service                                   |

| Figure 6-4.  | CPU Lookup CPU Miss Service                                  |

| Figure 6-5.  | Simulated best-case throughput and latency                   |

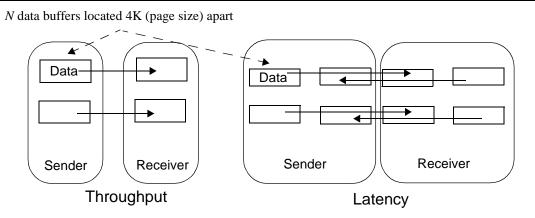

| Figure 6-6.  | Message operations in the microbenchmarks                    |

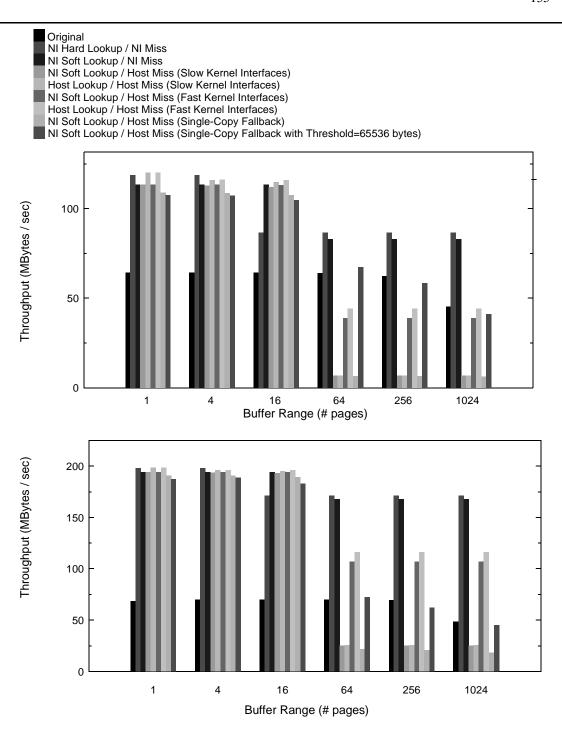

| Figure 6-7.  | Simulated throughput as a function of the buffer range       |

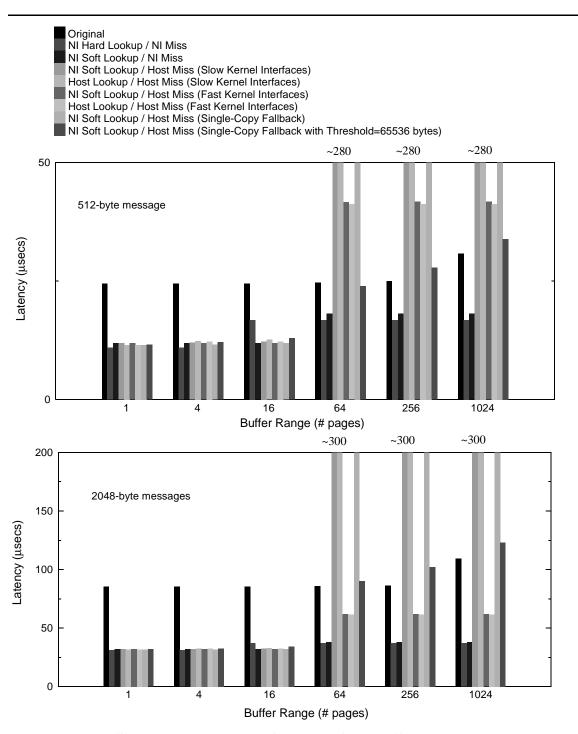

| Figure 6-8.  | Simulated latency as a function of the buffer range          |

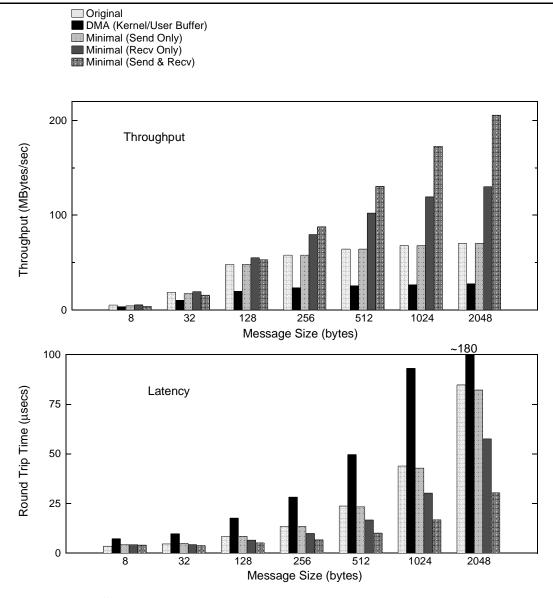

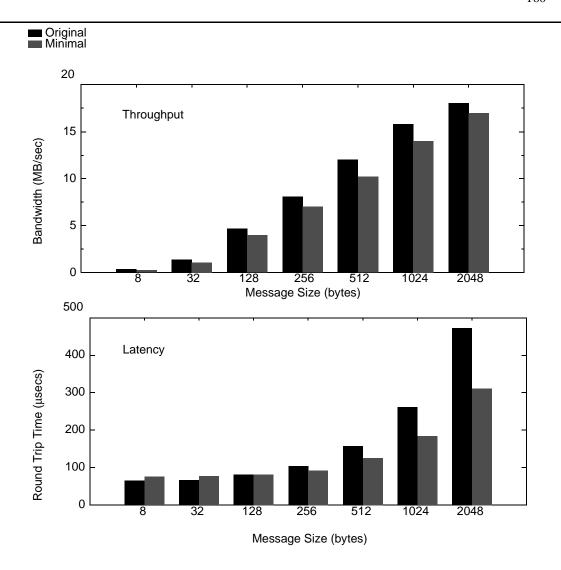

| Figure 6-9.  | Myrinet best-case throughput and latency                     |

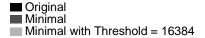

| Figure 6-10. | Myrinet latency as a function of the buffer range            |

| Figure A-1.  | Resources in a FGDSM system                                  |

| Figure A-2.  | Sample Application Makefile                                  |

| Figure A-3.  | Sample Library Makefile                                      |

# **List of Tables**

| Table 1.1: | Parallel programming platforms vs. parallel programming models 6         |

|------------|--------------------------------------------------------------------------|

| Table 2.1: | Classification of memory attributes according to name and content 20     |

| Table 2.2: | Breakdown of the time required to set invalid ECC                        |

| Table 2.3: | Access check overhead for uniprocessor runs of parallel applications 44  |

| Table 2.4: | Access change overheads with different fine-grain tag implementations 46 |

| Table 2.5: | Access fault overheads for different access types                        |

| Table 2.6: | Fine-grain access control overhead for common protocol actions 48        |

| Table 3.1: | A classification of user protocol in terms of buffer requirements 62     |

| Table 4.1: | Remote memory latency                                                    |

| Table 4.2: | Remote and local memory bandwidth                                        |

| Table 4.3: | Applications and input parameters                                        |

| Table 4.4: | Base system speedups for sixteen uniprocessor nodes95                    |

| Table 4.5: | Stache statistics                                                        |

| Table 4.6: | Message Statistics                                                       |

| Table 5.1: | Overheads in uniprocessor and SMP-node implementations of Blizzard 122   |

| Table 5.2: | Protocol traffic (in KB) per node as we change the clustering degree 124 |

| Table 5.3: | Applications and input parameters                                        |

| Table 5.4: | Base system speedups for 16 uniprocessor nodes                           |

| Table 6.1: | Classification of Address Translation Mechanisms                         |

| Table 6.2: | Simulation Node Parameters                                               |

| Table 6.3: | Simulation Address Translation Parameters                                |

| Table 6.4: | Myrinet Node Parameters                                                  |

| Table A.1: | Result of memory operations                                              |

# Chapter 1

## Introduction

This thesis proposes fine-grain distributed shared memory (FGDSM) systems on clusters of workstations (COWs) to support parallel programs and it explores the issues involved in the design and implementation of FGDSM systems on clusters of commodity workstations running commodity operating systems. FGDSM systems rely on fine-grain access control to selectively restrict memory accesses to cache-block-sized memory regions.

The thesis presents Blizzard, a family of FGDSM systems running on the Wisconsin Cluster Of Workstations. Blizzard supports the Tempest interface [Rei94] that implements shared memory coherence as user-level libraries. In this way, application-specific protocols can be developed to eliminate the overhead of fine-grain access control.

This section is organized as follows. Section 1.1 discusses the context for this work and places Blizzard in perspective to other approaches to support parallel programs. Section 1.2 presents an overview of the COW platform and discusses the structure of Blizzard. Finally, Section 1.3 presents a brief summary of the most important points in the main chapters of the thesis.

# 1.1 Fine-Grain Distributed Memory In Perspective

One of the most persistent themes in the history of computing has been the effort to harness the power of many processing units to accomplish a single task faster than using a single unit. Unlike sequential computing where the *von Neumann* model [BGvN46] has been dominant right from the start, no consensus has ever been reached on how to organize and control many activities for a single purpose. Numerous parallel programming models have been proposed to

facilitate this goal. Equally numerous parallel programming languages and programming environments have been developed to support specific parallel programming models.

Among parallel programming models, shared memory is popular because it provides a natural extension to the sequential programming model. Another popular programming model is message-passing, which exposes the inherent nature of a parallel platforms as a collection of processing units connected with a network through which they can exchange messages. Other approaches, such as data-parallel models, hide the parallel nature of the machine. They focus on extracting available parallelism using high-level constructs that define operations for vector variables. More exotic schemes such as dataflow models advocated a complete overhaul of the *von Neumann* model in favor of the programmer directly specifying the data dependency graph.

The lack of consensus at the basic level of the programming models is obvious in the history of the parallel computing platforms. System designers diverged to a greater or lesser extent from the *von Neuman* model in an attempt to directly support different parallel programming models. After more than thirty years of exploring alternative avenues, some consensus has been reached on the general form of parallel platforms. System designers have realized that you have to follow the performance curve of the microprocessors very closely and the size of the parallel market is not large enough to amortize the high fixed costs associated with the development of completely new hardware. System designers today agree that parallel machines should use commodity components (e.g., standard microprocessors). There two prevalent design approaches in building parallel platforms out of commodity processors. The first approach advocates hardware support for shared memory. The second approach prefers to connect processing nodes, each containing commodity microprocessors and memory, with a fast network.

Due to the popularity of the shared memory model, many system designers include in their platforms hardware support for shared memory. At the low-end, shared memory is becoming ubiquitous in the form of small-scale symmetric multiprocessors (SMPs). In these platforms, the processors are attached on the same memory bus. Both commodity microprocessors and system logic are specifically designed to support shared memory using bus-based coherence protocols [SS86]. Consequently, it becomes easy to build low-end shared memory systems since the fixed design costs are amortized over the large sales volumes of commodity microprocessors. Therefore, these systems are achieving cost-performance superior to their uniprocessor counterparts.

Supporting shared memory beyond a small number of processors however, requires extensive custom hardware support due to inherent scalability bottlenecks of bus-based shared memory. Both physical limitations and the non-linear cost of memory bus bandwidth prevents SMPs from scaling directly to a large number of processors. High-end shared memory servers extend the bus-based coherence protocols across many SMP nodes using custom system logic. Most often, the system logic implements the distributed shared memory (DSM) paradigm that provides a shared-memory abstraction over the physically distributed memory in a parallel

machine. Many recent commercial systems such as Sequent STiNG [LC96] and SGI Origin [LL97] follow this approach. However, the associated fixed design costs lead to high premiums charged for these shared memory platforms.

A less costly way to realize the performance potential of parallel processing is to connect commodity microprocessors using a custom low-latency network. These parallel platforms have been called massively parallel processors (MPPs). Since relatively little extra hardware except the custom network is required, this approach has enjoyed popularity in older machines such as Intel iPSC860 [Int90] and TMC CM-5 [Thi91]. It is still present today in commercial systems such as IBM SP-2.

At a high level of detail, there is not much difference between MPPs and a collection of workstations with the exception of the custom network. Recently however, the network technology has caught up with the other components of a workstation, prompting researchers to advocate using networks of workstations (NOWs) as parallel "minicomputers" [ACP95]. NOWs can take advantage of commodity components to a greater extent than MPPs. Not only commodity microprocessors can be used, but all the system components including backplane busses, system logic, and peripherals can now be off the self equipment.

My thesis refers to networks of workstations as clusters of workstations (COWs). The difference between NOWs and COWs is more perceived than real. Berkeley, which coined the NOW term, envisioned NOWs as desktop workstations that can be used as a parallel platform when idle. In contrast, COWs are assumed to be workstations that are used as a dedicated platform for running sequential and parallel applications. In this way, job scheduling issues become less important. Moreover, you do not have to pay the overheads associated with implementing process migration policies that are necessary in the NOW environment. Nevertheless, such issues are orthogonal to the ones addressed in this thesis. Therefore, in my thesis, the two terms are considered interchangeable.

A key factor that enables the use of commodity network equipment in NOWs has been that the emergence of interfaces that provide protected user-level access to the network interface (NI), so the operating system need not be invoked in the common case (user-level messaging). Commercial designs such as Myricom Myrinet [BCF<sup>+</sup>95], DEC Memory Channel [GCP96], Tandem TNet [Hor95] have become widely available. Collectively, these designs have been called system-area networks [Bel96] to distinguish them from traditional local area networks that have higher messaging overheads. System-area networks also enable the construction of clustered shared memory servers targeted for high availability and scalability.

Due to the proliferation of parallel programming models and computing platforms, portability of parallel programs remains a significant concern for parallel programs. The emergence of standard message-passing libraries, such as PVM and MPI [GBD<sup>+</sup>94, For94], that have been implemented both for message-passing and shared memory platforms has addressed the portability issue for message-passing programs.

Shared memory has been limited to page-based systems [LH89,CBZ91]. *Shared virtual memory* (SVM) [LH89,CBZ91] is the most common form of software DSM and implements coherence at page granularity using standard address translation hardware found in commodity microprocessors. Such systems suffer from fragmentation and false sharing and can perform poorly in the presence of fine-grain sharing [EK89]. For acceptable performance, page-based systems often resort to weaker shared memory consistency models [KDCZ93,ENCH96,KHS+97,YKA96].

Shared virtual memory systems lack *fine-grain access control*, a key feature of hardware shared memory machines. Access control is the ability to selectively restrict reads and writes to memory regions. At each memory reference, the system must perform a *lookup* to determine whether the referenced data is in local memory, in an appropriate state. If local data does not satisfy the reference, the system must invoke a *protocol action* to bring the desired data to the local node. We refer to the combination of performing a lookup on a memory reference and conditionally invoking an action as *access control*. Access control *granularity* (also referred to as the *block size*) is the smallest amount of data that can be independently controlled. Access control is fine-grain if its granularity is similar to a hardware cache block (32-128 bytes).

FGDSM systems can implement fine-grain access semantics and the coherence protocol either in software or hardware. Hardware shared-memory machines achieve high performance by using hardware-intensive implementations, but this additional hardware is not available on message-passing platforms. Therefore, FGDSM systems on message-passing hardware must rely on techniques that require little or no additional hardware. Like SVM systems, these systems use address translation hardware to map shared addresses to local memory pages but enforce coherence at a finer granularity. FGDSM systems achieve performance competitive to SVM systems [ZIS<sup>+</sup>97] without having to resort to weak consistency models.

Blizzard/CM-5 [SFL<sup>+</sup>94], developed by the author and others for the TMC CM-5, was the first FGDSM system on messaging passing hardware. Blizzard/COW<sup>1</sup> [SFH<sup>+</sup>96], which is its direct descendant, was developed on the Wisconsin Cluster of Workstations (COW) and is the focus of this thesis. Digital's Shasta [SGT96] is another FGDSM system inspired by Blizzard/CM-5. Unlike Shasta, Blizzard uses the Tempest interface [Rei94] to support software distributed shared memory. Tempest separates the mechanisms required to implement distributed shared memory from the coherence protocols that enforce the shared memory semantics. By default, shared memory programs are linked against a library that implements an 128-byte S-COMA-like [HSL94] software protocol [RLW94] to maintain coherence across nodes.

Tempest's flexibility allows the implementation of application-specific custom coherence protocols [FLR<sup>+</sup>94] which integrate shared memory with messaging. Such protocols, called *hybrid* protocols, can reduce the overhead of fine-grain access control by being tailored to the

<sup>1.</sup> Throughout the thesis, Blizzard without qualification refers to the COW implementation. Blizzard/CM-5 is used to refer to the older Blizzard system.

application access patterns. In addition, Tempest provides an attractive target to build runtime systems for parallel languages [LRV94,CL96] where compilers can tailor the coherence protocol to incorporate high-level knowledge about the application access patterns. While other hardware shared memory systems integrate message passing and shared memory [HGDG94], none offers the same flexibility to develop application-specific protocols as user (rather than system) libraries.

High-end Tempest implementations such as the Typhoon designs [RLW94,RPW96] include extensive hardware support for fine-grain access control and protocol actions. Such designs achieve performance competitive to other hardware shared memory approaches [RPW96] but still offer Tempest's flexibility to support coherence protocols. Blizzard, however, implements coherence in software but maintains fine-grain access semantics either in software or hardware using mostly commodity hardware and software. Tempest's flexibility to support custom coherence protocols is especially important for Blizzard since the overhead of fine-grain access control, protocol actions, and messaging is higher with Blizzard than it is in hardware-intensive Tempest implementations. Blizzard also demonstrates the portability provided by the Tempest interface. Tempest allows clusters to support the same shared-memory abstraction as supercomputers, just as MPI and PVM support a common interface for coarse-grain message passing.

Table 1.1 summarizes the relationships between parallel programming models and parallel programming platforms as we have discussed them in this section. Modern parallel machines are designed using commodity microprocessors to directly support message-passing or shared memory. Hardware shared memory machines (SMPs, DSMs) can effectively—but not optimally—support message-passing or hybrid programming models through emulation. Experimental designs including Tempest high-end implementations better integrate shared memory and message-passing. Tempest implementations, however, are the only ones that support application-specific protocols as user-level libraries. Blizzard's domain is existing message-passing platforms such as MPPs, COWs, or clustered servers. In this domain, message-passing is directly supported by message-passing libraries. Shared memory, however, requires software with little or no additional hardware. Blizzard has the following two advantages over other approaches.

- It supports fine-grain shared memory programs as efficiently as SVM systems without having to resort to weaker consistency models.

- It supports the Tempest interface, which allows the development of application-specific hybrid coherence protocols, tailored to the application access patterns.

#### 1.2 System Overview

This section presents background information on the Wisconsin COW platform, Blizzard's components, the Tempest interface, and Tempest's default shared memory coherence protocol (stache).

Table 1.1: Parallel programming platforms vs. parallel programming models.

| Parallel Platform               |                                             | Programming Model                                       |                                                                   |                              |

|---------------------------------|---------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|------------------------------|

|                                 |                                             | Shared<br>Memory                                        | Message<br>Passing                                                | Hybrids                      |

| Shared<br>memory<br>hardware    | Existing<br>SMPs<br>&DSMs                   | Direct support<br>(designed)                            | Through shared memory                                             | Through shared memory        |

|                                 | Experimental DSMs: Typhoon (Flash, Alewife) | Direct support<br>(designed)                            | Direct support<br>(designed)                                      | Direct support<br>(designed) |

| No shared<br>memory<br>hardware | Message<br>passing<br>(PVM, MPI,<br>AM)     | -                                                       | Direct support<br>(designed)                                      | -                            |

|                                 | Page based<br>DSMs                          | Poorly without<br>weak<br>consistency                   | -                                                                 | -                            |

|                                 | FGDSMs                                      | Competitive to page-based DSMs without weak consistency | -                                                                 | -                            |

|                                 | Blizzard                                    | Direct support<br>(similar to<br>FGDSMs)                | Direct support<br>(similar to<br>message<br>passing<br>libraries) | Direct support               |

## 1.2.1 Wisconsin Cluster Of Workstations

The Wisconsin COW consists of 40 dual-processor Sun SPARCStation 20s. Each contains two 66 Mhz Ross HyperSPARC processors [ROS93] with a 256 KB L2 cache memory and 64

MB of memory. The cache-coherent 50 Mhz MBus connects the processors and memory. I/O devices are on the 25 Mhz SBus, which a bridge connects to the MBus. SPARCStation 20s provide an I/O virtual address space for Sbus devices with a separate MMU in the MBus-to-SBus bridge. The I/O MMU maps 32 bit Sbus addresses to 36 bit Mbus addresses using a one-level page table. Under Solaris 2.4, the I/O MMU directly maps kernel virtual addresses to Sbus virtual addresses, which limits DMA operations to the kernel address space. The operating system of the COW nodes is Solaris 2.4.

Each COW node contains a custom-built Vortex card [Pfi95] and a Myrinet network interface [BCF<sup>+</sup>95]. The Vortex card plugs into the MBus and performs fine-grain access control by snooping bus transactions. Each node also contains a Myrinet interface, which consists of a slow (7–8 MIPS) custom processor (LANai -2) and 128 KBytes of memory. The LANai performs limited protocol processing and schedules DMA transfers between the network and LANai memory or LANai memory and SPARC memory. The LANai processor cannot access SPARC memory directly using loads and stores. However, it can move data using DMA operations. Moreover, it can interrupt the host processor. The Myrinet switches are connected in a tree topology with the nodes attached as leaves of the tree.

Jobs intended to run on the COW processing nodes are submitted through the *Distributed Job Manager* (DJM) [Cen93]. The version of DJM running on the COW is based on the CM-5 1.0 version, but it has been heavily modified for the COW environment by Mark Dionne [Dio96].

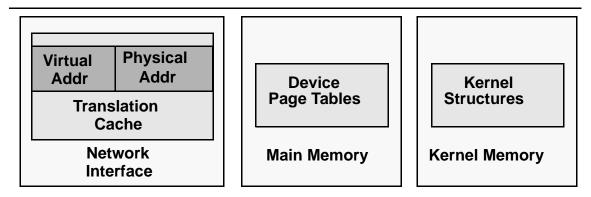

#### 1.2.2 Blizzard and FGDSM Resources

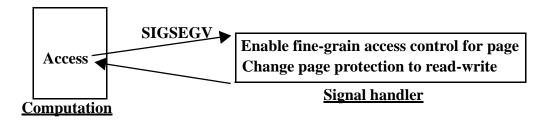

In Blizzard, shared memory is supported only for regions allocated through special *malloc()*-like calls that manage a shared heap<sup>1</sup>. Blizzard preallocates an address range within the application address space for the shared heap (Figure 1-1). Initially, accesses to the shared region are disabled by setting the page protection to *none* for all the pages in the region. On the first access to a page in the shared heap, a fault occurs which the operating system forwards to a Blizzard signal handler. Tempest specifies user-level page fault handlers and exports primitives which toggle the page protection to read-write and enable file-grain access control for that page.

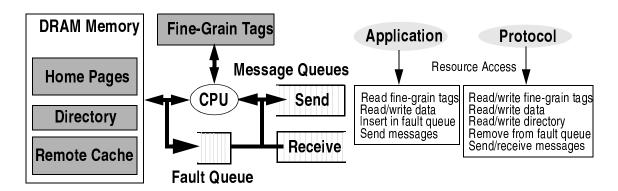

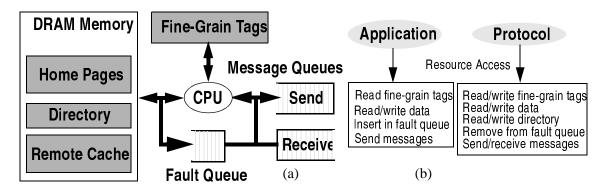

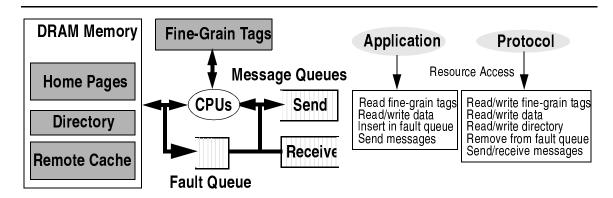

Figure 1-2 illustrates the resources required to implement FGDSM systems. Shared data pages are distributed among the nodes, with every node serving as a designated *home* for a group of pages. A *directory* maintains sharing status for all the memory blocks on the home nodes. A *remote cache* serves as a temporary repository for data fetched from remote nodes. A set of *fine-grain tags* enforce access semantics for shared remote memory blocks. Upon access violation, the address of the faulting memory block and the type of access are inserted

<sup>1.</sup> Blizzard supports the PARMACS programming model [BBD<sup>+</sup>87]. PARMACS offers to each process of a parallel application a private address space with *fork*-like semantics. Shared memory support is limited to the special shared heap.

Figure 1-1. Process address space and initialization of shared pages.

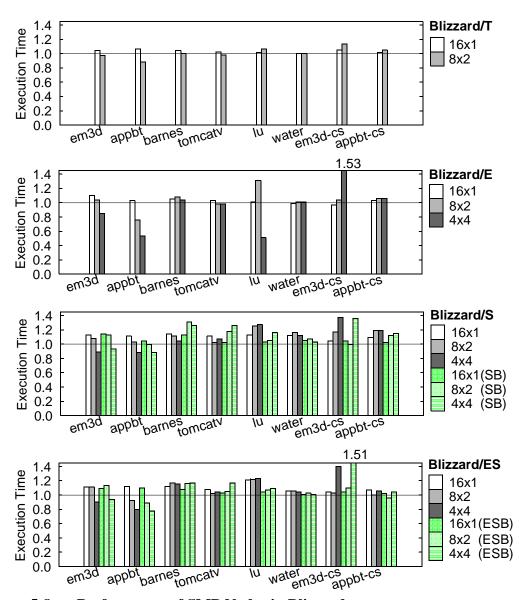

in the *fault queue*. Processor(s) are responsible for running both the application and the software coherence protocol that implements shared memory. The protocol moves memory blocks among the nodes using *send message queues* and *receive message queues*.

Figure 1-2 also illustrates a breakdown of the resources accessed by the application and the protocol respectively. An application verifies access semantics upon a memory operation by reading the fine-grain tags. Memory operations also may read or write data to either home pages or the remote cache. An access violation in the application will insert an entry into the fault queue. The protocol manipulates the fine-grain tags to enforce access semantics to shared data, manages the remote cache data and state, maintains the list and status of sharers in the directory, removes entries from the fault queue, and sends and receives messages.

Figure 1-2. Resources in a software FGDSM system.

#### 1.2.3 Tempest

Tempest is an interface that enables user-level software to control a machine's memory management and communication facilities [Rei94]. Software can compose the primitive mechanisms to support either message-passing, shared-memory, or hybrid applications. Since these primitives are available to programs running at user level, a programmer or compiler can tailor memory semantics to a particular program or data structure, much as RISC processors enable compilers to tailor instruction sequences to a function call or data reference [Wul81]. Tempest provides four types of mechanisms:

**Virtual Memory Management.** With user-level virtual-memory management, a compiler or run-time system can manage a program's address space. Tempest provides memory mapping calls that the coherence protocol uses to manage a conventional flat address space. In the context of a commodity operating system, this mechanism is trivially implemented using system calls that change the page protection for the shared heap.

**Fine-Grain Access Control.** Fine-grain access control is the Tempest mechanism that detects reads or writes to invalid blocks or writes to read-only blocks and traps to user-level code, which uses the resulting exceptions to execute a coherence protocol action [HLW95]. At each memory reference, the system must ensure that the referenced datum is local and accessible. Therefore, each memory reference is logically preceded by a check that has the following semantics:

```

if (!lookup(Address))

CallHandler(Address, AccessType)

memory-reference(Address)

```

If the access is allowed, the reference proceeds normally. Otherwise, the shared-memory protocol software must be invoked. This sequence must execute atomically to ensure correct-

ness. In the Tempest model, fine-grain access control is based on tagged memory blocks. Every memory block—an aligned, implementation-dependent, power-of-two size region of memory—has an access tag of *ReadWrite*, *ReadOnly*, or *Invalid* that limits the allowed accesses. Reads or writes to a *ReadWrite* block or reads to a *ReadOnly* block complete normally, but an access to an *Invalid* block or a write to a *ReadOnly* block causes a block access fault. These faults are similar to page faults. They suspend the thread making the access and invoke a user-level handler. A typical handler performs the actions dictated by a coherence protocol to make the access possible and updates the tag. Then the access is retried.

**Low-Overhead Messaging.** Low-overhead "active" messages [vECGS92] provide low-latency communication, which is fundamental to the performance of many parallel programs. In Tempest, a processor sends a message by specifying the destination node, handler address, and a string of arguments. The message's arrival at its destination creates a thread that runs the handler, which extracts the remainder of the message with *receive* calls. A handler executes atomically with respect to other handlers, to reduce synchronization overhead.

**Bulk Data Transfers.** Efficient transfers of large quantities of data is critical for many applications. In Tempest, a processor initiates a bulk data transfer much as it would start a conventional DMA transaction, by specifying virtual addresses on both source and destination nodes. The transfer is logically asynchronous with the computation.

#### 1.2.4 Stache

Tempest's default coherence protocol is an 128-byte S-COMA-like [HSL94] software protocol [RLW94] called stache. Stache maintains internal data structures to correctly implement a sequentially consistent shared memory coherence protocol.

For each shared page, one node acts as the home node. By default, home pages are distributed among the nodes in a round-robin manner, but sophisticated programs are able to optimize the allocation using a first-touch policy. With this policy, all home pages are allocated on the first node during the initialization phase. After the parallel phase begins, any access to a page by a node, will result in that node becoming the home node for the page. This allocation policy results in improved performance because normally stache is a four-hop protocol unless the home node is one of the sharer nodes. More specifically, the first time that some node other then the home node accesses a memory location in a page, it will fault. The stache fault handler will request a copy of the block from the home node. If the block is not available at the home node, it will be forwarded to the node that has the most recent copy. That node will send the block back to the home. From there, it will be forwarded to the requesting node. Since there four messages are required to service this request, stache is a four-hop protocol. If no other nodes were involved only two messages need to be exchanged.

#### 1.3 Thesis Overview

The thesis examines the issues involved in supporting fine-grain shared memory in clusters of workstations. The thesis organization is as follows. Chapter 2 discusses fine-grain access control implementations on commodity workstations. Chapter 3 discusses issues in the design of messaging subsystems for FGDSM systems. Chapter 4 presents performance results and evaluates Blizzard as a platform for parallel applications. Chapter 5 discusses the advantages of multiprocessor workstations for FGDSM systems. Chapter 6 discusses address translation in network interfaces to support zero-copy messaging directly to user data structures. Chapter 7 presents a summary of the thesis, discusses the implications of this work and points to possible future directions. A brief summary of the main points in each chapter of the thesis follows.

Chapter 2 investigates fine-grain access control implementations on commodity workstations. It presents four different fine-grain tag implementations with different performance characteristics. The first, Blizzard-S, adds a fast lookup before each shared-memory reference [LW94] by modifying the program's executable [LB94]. The second, Blizzard-E, uses the memory's error-correcting code (ECC) bits as valid bits and the page protection to emulate read-only bits [RFW93]. The third, Blizzard-ES, combines the two techniques using software lookups for stores and ECC for loads [SFL+94]. The fourth, Blizzard/T, uses Vortex, a custom fine-grain access control accelerator board. The board was originally developed by members of the Wisconsin WindTunnel project [Pfi95] to demonstrate the simplest possible hardware Tempest implementation (Typhoon-0 [RPW96]). Blizzard/T explores the Vortex's ability to support hardware fine-grain tags modified without kernel intervention but unlike Typhoon-0, it does not use any of its other abilities to accelerate Tempest operations (e.g., mechanisms to accelerate dispatch of access fault handlers).

Chapter 2 makes the following three contributions.

- First, it identifies fine-grain access control as a memory property that can be associated either with the physical or the virtual memory. It argues that the fine-grain access control tags should be associated with the physical address space for performance, but physical addresses should not be exposed to the user so that the kernel is not restricted in changing the binding of virtual to physical addresses.

- Second, it describes the kernel support that the hardware techniques require to access hardware resources beyond those the operating system was designed to support. Blizzard's kernel support offers extended kernel functionality through runtime-loadable modules, follows a modular approach, and optimizes all the performance-critical operations.

- Third, it presents low-level performance results to evaluate the different Blizzard fine-grain access control implementations.

**Chapter 3** investigates messaging subsystem design for FGDSM systems. For standard shared memory coherence protocols, where data are transferred in cache-block sized quantities, low-latency communication is critical to the performance of many parallel programs. For application-specific protocols, where the coherence protocol has been optimized to fit the

application communication requirements, high bandwidth is of equal concern to low latency. Tempest's messaging interface is based on the Berkeley active messages [vECGS92], but it differs in two important aspects, necessary to use Tempest messages to implement *transparent* shared memory protocols. Tempest messages are not constrained to follow a request-reply protocol and are delivered without explicit polling by an application program.

Chapter 3 makes the following four contributions.

- First, it develops a methodology to compute the buffer requirements for an arbitrary messaging protocol. Using this methodology, it shows that shared memory coherence protocols, while not pure request/reply protocols, have bounded buffer requirements.

- Second, it evaluates buffer allocation policies for active message implementations. It proposes a buffer allocation policy that does not require buffers in a node's local memory in the common case, yet is robust enough to handle arbitrary traffic streams.

- Third, it evaluates different solutions to avoid explicit polling and it proposes implicit polling using binary rewriting to insert polls in the application code.

- Fourth, it present performance results that indicate that the extended functionality does not affect performance adversely.

**Chapter 4** presents performance results to evaluate Blizzard as a platform for running parallel applications. For this task, both low-level microbenchmarks and application benchmarks are used. The performance results suggest that parallel applications with small communication requirements easily achieve significant speedups using transparent shared memory. Parallel applications with high communication requirements however, require application-specific coherence protocols, selectively employed on the performance-critical data structures. Moreover, the results show that application-specific protocols are particularly appropriate for FGDSM systems on low-cost platforms because their relative performance benefit is significantly higher than other proposed tightly-integrated high-end Tempest implementations.

Chapter 5 investigates extending FGDSM systems to networks of multiprocessor workstations. FGDSMs are particularly attractive for implementing distributed shared memory on clusters of multiprocessor workstations because they transparently—i.e., without the involvement of the application programmer—extend the fine-grain hardware shared-memory abstraction across a cluster. Grouping processors into multiprocessor nodes allows them to communicate within the node using fast hardware shared-memory mechanisms. Multiple processors can also improve performance by overlapping application execution with protocol actions. However, simultaneous sharing of node's resources (e.g., memory) between the application and the protocol requires mechanisms for guaranteeing atomic accesses [SGA97]. Without efficient support for atomicity, accesses to frequently shared resources may incur high overheads and result in lower performance with multiprocessor nodes.

Chapter 5 makes the following two contributions.

• First, it identifies the shared resources in FGDSM systems to which access should be controlled in an multiprocessor environment and it proposes techniques to address the syn-

- chronization issues for each resource based on the frequency and type of accesses to that resource.

- Second, it compares the performance of Blizzard's uniprocessor-node and multiprocessor-node implementations while keeping the aggregate number of processors and amount of memory constant. The performance results suggest that grouping processors: (i) results in competitive performance while substantially reducing hardware requirements, (ii) benefits from custom hardware support for fine-grain sharing, (iii) boosts performance in FGDSMs with high-overhead protocol operations, and (iv) can hurt performance in pathological cases due to the ad hoc scheduling of protocol operations on a multiprocessor node.

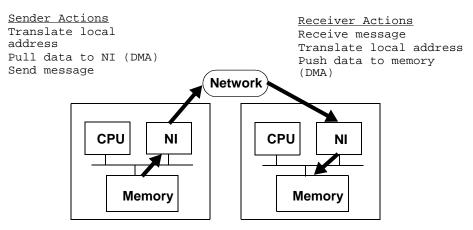

Chapter 6 investigates address translation mechanisms in network interfaces to support zero-copy messaging directly to user data structures and avoid redundant data copying. Good messaging performance is important for application-specific protocols that push the limits of the messaging hardware. For zero-copy messaging, the network interface must examine the message contents, determine the data location and perform the transfer. The application accesses data using virtual addresses, which can be passed to the interface when the message operation is initiated. However, the network interface accesses memory using physical addresses, so the virtual address known by the application must be translated to a physical address usable by the network interface.

Chapter 6 makes the following four contributions.

- First, it presents a classification of address translation mechanisms for network interfaces, based on where the lookup and the miss handling are performed.

- Second, it analyzes the address translation design space and it evaluates a series of designs

with increasingly higher operating system support requirements. For each design point, it

determines whether it can accelerate messaging and whether it degrades gracefully once

the translation structures thrash, considers the required operating support and proposes

techniques for graceful degradation in the absence of appropriate operating system interfaces.

- Third, it provides performance data from simulations that demonstrate that even without operating system support, there exist solutions so that the performance properties hold.

- Fourth, it demonstrates the feasibility of the approach by presenting experimental results from an implementation on real hardware within the Blizzard framework.

# Chapter 2

# **Fine Grain Access Control**

Fine-grain access control is a fundamental operation in shared memory systems [SFL<sup>+</sup>94]. Regardless of how shared memory is implemented, memory accesses are checked against the current coherence protocol state and protocol actions are initiated to deal with accesses that are not allowed in terms of the protocol state. Blizzard provides shared memory and consequently, must implement these two operations. The design and implementation of Blizzard's fine-grain access control mechanisms is the focus of this chapter.

Blizzard supports the Tempest interface [Rei94], which exposes fine-grain access control tags to user level, allowing shared memory coherence protocols to be implemented as user-level libraries. Tempest's fine-grain access control mechanism detects reads or writes to invalid blocks or writes to read-only blocks and traps to user-level code, which uses the resulting exceptions to execute a coherence protocol action in software [HLW95]. At each memory reference, the system must ensure that the referenced datum is local and accessible. If the access is allowed, the reference proceeds normally. Otherwise, the shared-memory protocol software must be invoked, which is achieved by suspending the computation and invoking a user-level handler. A typical handler performs the actions dictated by a coherence protocol to allow the access and then resumes the computation.

The fine-grain access control mechanism is similar to full/empty bits of dataflow architectures [DCF<sup>+</sup>89] but it is tailored to support the implementation of shared memory protocols. For this reason, it extends the two-state model of the full/empty bits to a three-state model that includes a readonly state. More specifically, Tempest's fine-grain access control is based on tagged memory blocks. Every memory block (an aligned, implementation-dependent, power-of-two size region of memory) has an access tag of *ReadWrite*, *ReadOnly*, or *Invalid*

that limits the allowed accesses. For example, reads or writes to a *ReadWrite* block or reads to a *ReadOnly* block complete normally. However, an access to an *Invalid* block or a write to a *ReadOnly* block causes an access fault.

The performance of a shared memory implementation depends both on the overheads of the access check and the protocol action operations. Depending on how these operations are implemented, they will have different performance, cost and design characteristics. We can classify the implementation techniques in software, hardware or combination approaches. Hardware techniques provide better performance than software techniques but at a higher cost point. Since the access check and the protocol action allow different implementations, system designers can follow alternative paths in the design space. Blizzard represents a low cost design point that relies mainly on software to implement these operations. This chapter reviews the design space and places Blizzard into perspective to other approaches.

Since Tempest exposes fine-grain access control tags to the user level, the fine-grain access control information becomes user-visible and modifiable state. This state is a attribute that accompanies the application memory and therefore, it must be integrated within other abstractions related to memory. More specifically, general purpose operating systems virtualize the physical memory: user processes do not directly refer to physical memory but instead, they use addresses that refer to a virtual address space. Virtual memory references from applications are translated to physical memory references by the address translation hardware of modern processors. Consequently, memory properties are associated either with the physical or the virtual memory. The question arises with which one should we associate fine-grain access control. I argue that the fine-grain tags should be associated with the physical address space for performance, but physical addresses should not be exposed to the user and used to refer to the tags so that the kernel is not restricted in changing the binding of virtual to physical addresses.

Blizzard implements fine-grain access control using a variety of techniques. Common to all techniques is that the protocol actions are executed on the node processors in software. What differentiates these techniques is the way with which the fine-grain access control tags are implemented. We can distinguish software and hardware techniques. The software techniques rely on explicit checks inserted in the instruction stream to enforce the appropriate semantics. The hardware techniques use commodity or custom hardware to accomplish the same task while avoiding the overhead of explicit access checks.

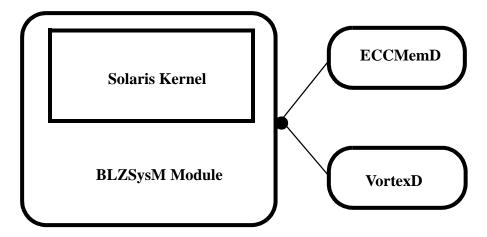

Hardware techniques require kernel support to access hardware resources beyond those the operating system was designed to support. Blizzard runs under a Solaris 2.4 kernel, which it extends to support hardware fine-grain access control. The following three design principles characterize this effort. First, a constant constraint is the use of an unmodified commodity kernel. Extended functionality is offered through runtime-loadable kernel object modules. Second, a modular approach is followed. A hardware-independent module extends internal kernel interfaces while hardware-specific device drivers rely on its services to support specific hardware techniques. Third, all the performance-critical operations are extensively optimized.

The rest of this chapter is organized as follows. Section 2.1 discusses fine-grain access control as a fundamental operation in shared memory systems. Moreover, it defines a design space for its implementation, in which Blizzard is placed. Section 2.2 portrays fine-grain access control as a memory attribute and discusses its integration within the existing memory abstractions. Section 2.3 focuses on the software and hardware techniques employed by Blizzard to provide fine-grain access control in the Wisconsin Cluster Of Workstations (COW). Section 2.4 presents the kernel support for hardware fine-grain access control, which has been implemented in Sun's Solaris 2.4 operating system. Section 2.5 presents low level performance results to evaluate the different fine-grain tag implementations. Section 2.6 finishes the chapter with the conclusions of this study.

### 2.1 Fine Grain Access Control Design Space

Fine-grain access control can be implemented in many ways. The lookup of the current state and/or the protocol action can be performed in either software, hardware, or a combination of the two. These alternatives have different performance, cost, and design characteristics. This section classifies access control techniques based on where the lookup is performed and where the action is executed, and places Blizzard within the design space.

Either software or hardware can perform the access check. A software lookup avoids the expense and design cost of hardware, but incurs a fixed overhead on each lookup. Hardware typically incurs no overhead when the lookup does not invoke an action. Lookup hardware can be placed at almost any level of the memory hierarchy: TLB, cache controller, memory controller, or a separate snooping controller.

When a lookup detects a conflict, it must invoke an action dictated by a coherence protocol to obtain an accessible copy of a block. As with the lookup itself, hardware, software, or a combination of the two can perform this action. With software, the protocol action can execute either on the same processors as the application or on a dedicated processor.

Tempest differs from other approaches to shared memory because it exposes fine-grain access control to user level. This allows the implementation of coherence protocols as user-level libraries written in a general-purpose programming language. The extra flexibility however, restricts possible implementations to designs where the protocol actions are executed in an environment sufficiently similar to the one that the computation is executing (i.e., a processor).

Reinhardt, et al., have shown that the overheads to support user-level coherence protocols do not inhibit high-end Tempest implementations, such as the proposed Typhoon designs, from being competitive to dedicated hardware solutions [RPW96,Rei96]. Such implementations, targeted for the server market, emphasize performance over cost. These systems provide hardware support for both the access control test and protocol action. For example, a dedicated processor for protocol actions can minimize invocation and action overhead while still exploiting commodity computation processors. However, this approach requires either a com-

plex ASIC or full-custom chip design, which significantly increases design time and manufacturing cost.

Blizzard and Digital's Shasta [SGT96], on the other hand, are FGDSM systems targeted toward networks of workstations or personal computers. In such environments, the cost and complexity of additional hardware is more important because they must compete on uniprocessor cost/performance. Blizzard relies mainly on commodity software and hardware to provide fine-grain access control. However, simple custom hardware support for the access test can be cost-effective and therefore, it is also considered. Previous approaches to shared memory on networks of workstations mainly targeted page-based distributed shared memory (DSM) systems [LH89]. Such systems required relaxed memory consistency models, which complicate the programming model, to overcome the effects of false sharing and fragmentation and offer acceptable performance [KDCZ93]. Zhou, et al., however, have shown that sequentially consistent fine-grain DSM systems are competitive with page-based systems that support weaker consistency models [ZIS<sup>+</sup>97].

Blizzard explores four different fine-grain tag implementations. These designs cover a substantial range of the design space for fine-grain access control mechanisms [SFL<sup>+</sup>94]. Blizzard/S uses a software method based on locally available executable-editing technology [LS95]. Blizzard/E uses commodity hardware to accelerate the access check. The memory controller supports *Invalid* blocks while the TLB is used to emulate *ReadOnly* blocks. Blizzard/ES also uses the memory controller for *Invalid* blocks but relies on the same software method as Blizzard/S for *ReadOnly* blocks. Finally, Blizzard/T uses Vortex, a custom board [Pfi95] to accelerate many fine-grain access control operations.

We shall subsequently review alternative techniques to implement the access check (Section 2.1.1) and alternative locations to execute the protocol actions (Section 2.1.2).

#### 2.1.1 Access Check

**Software.** The code in a software lookup checks a main-memory data structure to determine the state of a block before a reference. Static analysis can detect and potentially eliminate redundant tests or even batch accesses to the consecutive cache blocks as in Shasta [SGT96]. Either a compiler or a program executable editing tool [LB94,LS95] can insert software tests. With the latter approach every compiler need not reimplement test analysis and code generation. Blizzard/S and Shasta [SGT96] also follow this approach (Section 2.3.1). Compiler-inserted lookups can exploit application-level information. Orca [BTK90], for example, provides access control on program objects instead of blocks.

**Translation Lookahead Buffer (TLB).** Standard address translation hardware provides access control, though at memory page granularity. Nevertheless, it forms the basis of several distributed-shared-memory systems such as IVY [LH89], Munin [CBZ91] and TreadMarks [KDCZ93]. Blizzard/E partially relies on the TLB to emulate fine-grain access control (Section 2.3.2). Though unimplemented by current commodity processors, additional,

per-block access bits in a TLB entry could provide fine-grain access control. The "lock bits" in certain IBM RISC machines, including the 801 [CM88] and RS/6000 [OG90], provide access control on 128-byte blocks. Unfortunately, these bits can only partially support fine-grain access control since they do not provide the *ReadOnly* state. Tamir, et al., have proposed extensions to the format of the page table in order to fully support fine-grain access control [TJ92].

Cache Controller. The MIT Alewife [CKA91] and Kendall Square Research KSR-1 [Ken92] shared-memory systems use custom cache controllers to implement access control. In addition to detecting misses in hardware caches, these controllers determine when to invoke a protocol action. On Alewife, a local directory is consulted on misses to local physical addresses to determine if a protocol action is required. Misses to remote physical addresses always invoke an action. Due to the KSR-1's COMA architecture, any reference that misses in the remote memory cache requires protocol action. A trend toward on-chip second-level cache controllers [Hsu94] has made modified cache controllers incompatible with modern commodity processors such as the Pentium Pro [Int96] and PowerPC 750 processors.

**Memory Controller.** If the system can guarantee that the processor's hardware caches never contain *Invalid* blocks and that *ReadOnly* blocks are cached in a read-only state, the memory controller can perform the lookup on hardware cache misses. This approach is used by Sun's S3.mp [NMP+93], NIMBUS's NIM 6133 [NIM93,SFL+94], and Stanford's FLASH [K+94]. S3.mp has a custom memory controller that performs a hardware lookup at every bus request. NIM 6133 integrates fine-grain access control with memory's error correction code. FLASH's programmable processor in the memory controller performs the lookup in software. It keeps state information in regular memory and caches it on the controller. Custom controllers are not possible, however, with many current processors. Blizzard/E and Blizzard/ES partially rely on existing support for error correction in commodity microprocessors. Microprocessor trends make it increasingly difficult to use this mechanism with many future microprocessors that cannot recover from late arriving exceptions in the lower levels of the memory hierarchy.

**Bus Snooping.** For economic and performance reasons, most hardware approaches avoid changes to commodity microprocessors. Nevertheless, most modern commodity processors support bus-based coherence protocols and therefore, implement fine-grain access control in the processor cache controller. Despite the progress in bus-based symmetric multiprocessors, evident in designs such as Sun's Enterprise Server 6000, the scalability of bus-based systems is ultimately limited. When a processor supports a bus-based coherence scheme, a separate bus-snooping agent can perform a lookup similar to that performed by a memory controller. Stanford DASH [LLG<sup>+</sup>92] and Typhoon [RLW94] among experimental designs, employ this approach. Many recent commercial shared memory machines, such as Sequent STiNG [LC96] and SGI Origin [LL97] also follow this approach.

#### 2.1.2 Protocol Action

**Custom Hardware.** High performance shared memory systems use dedicated hardware to execute the protocol actions. The list includes older systems like DASH, KSR-1, and S3.mp as well as newer systems like Convex Exemplar and SGI Origin. Dedicated hardware provides high performance for a single protocol. While custom hardware performs an action quickly, research has shown that no single protocol is optimal for all applications [KMRS88] or even for all data structures within an application [BCZ90,FLR<sup>+</sup>94]. Hybrid hardware/software protocols such as Alewife's LimitLESS [CKA91], Dir<sub>1</sub>SW [HLRW93], and Typhoon-2 [Rei96] implement the expected common cases in hardware and trap to system software to handle complex, infrequent events. High design costs and resource constraints make custom hardware unattractive. Nevertheless, as the relatively large number of commercially available systems suggests, system vendors believe that the costs are justified by the premiums charged for high-end systems.

**Primary processor.** Performing actions on the node processor(s) provides protocol flexibility and avoids the additional cost of custom hardware or a dedicated processor. Blizzard uses this approach as do page-based DSM systems such as IVY and Munin. However, interrupting an application to run an action can add considerable overhead. Alewife addressed this problem with a modified processor that supports rapid context switches. Blizzard implementations include extensive operating system support to minimize the context switch overhead.

**Dedicated processor.** FLASH, Sequent STiNG, and Typhoon achieve both high performance and protocol flexibility by executing actions on an auxiliary processor dedicated to that purpose. This approach avoids a context switch on the node processor(s) and may be crucial if the processor(s) cannot recover from late arriving exceptions in the lower levels of the memory hierarchy. In addition, an auxiliary processor can provide rapid invocation of action code, tight coupling with the network interface, special registers, and special operations. Of course, the design effort increases as the processor is more extensively customized. Blizzard can also dedicate a processor for execution of protocol actions. However, studies have shown that for networks of workstations this policy generally does not result in the best utilization of the processor [FW96,FW97,Fal97].

#### 2.2 Fine-Grain Access Control Abstraction