# ANALYSIS OF MULTI-MEGABYTE SECONDARY CPU CACHE MEMORIES

by

Richard Eugene Kessler

Computer Sciences Technical Report #1032

July 1991

# ANALYSIS OF MULTI-MEGABYTE SECONDARY CPU CACHE MEMORIES

by

## RICHARD EUGENE KESSLER

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Science)

at the

UNIVERSITY OF WISCONSIN-MADISON

1991

© copyright by Richard Eugene Kessler 1991 All Rights Reserved

# Analysis of Multi-Megabyte Secondary CPU Cache Memories

## Richard Eugene Kessler

This dissertation investigates multi-megabyte secondary caches. In a multi-level cache hierarchy, secondary caches service processor memory references that cannot be serviced by smaller and faster primary caches. With faster processors and expanding main memories, a multi-megabyte cache is increasingly vital because it shields processor memory references from costly main memory accesses, even when the processor references a large address space. Multi-megabyte secondary caches allow processors to execute at the speeds they are capable of, even when there is a large processor-to-main-memory speed gap.

This analysis uses a new collection of memory address traces that is appropriate for multimegabyte cache simulation. These traces thoroughly characterize several large workloads, and are long enough (billions of instructions) to overcome multi-megabyte cache cold-start. This dissertation includes the first comparison of two previously-proposed trace-sampling techniques that can reduce long-trace simulation requirements: set sampling and time sampling. Under a range of conditions, set sampling produces more accurate cache performance estimates with less trace data than time sampling.

This dissertation examines many alternative cache designs. It shows that multi-megabyte secondary caches are extremely useful with large processor-to-main-memory speed gaps. Furthermore, associativity is needed for smaller secondary caches, but may not be necessary in multi-megabyte caches; multi-megabyte cache block sizes should be larger than for smaller caches, and the block size that equals the fixed latency and transfer time miss penalty components is a good design point.

Finally, this dissertation introduces and solves the problems caused by the interaction of virtual memory and real-indexed multi-megabyte caches. Since the placement of pages in main memory also places data in the cache, a poor page placement will cause poor cache performance. This dissertation introduces several new *careful page mapping* algorithms to improve the page placement, and shows that they eliminate 10%-20% of the direct-mapped real-indexed cache misses for the long traces. In other words, this dissertation develops software techniques that can make a hardware direct-mapped cache appear about 50% larger.

## Acknowledgements

There are so many that helped put this dissertation together that I don't know where to start. Perhaps most importantly, I want thank the National Science Foundation and the University of Wisconsin Alumni Research Foundation for financially supporting my graduate career through fellowships. Digital Equipment also helped financially through an internship during the summer of 1989. My advisor, Mark Hill, was always a source of drive and inspiration. Mark patiently corrected many of the errors in this dissertation. The mistakes that remain in this dissertation, however, are mine. Without him, this thesis would not exist.

I also owe a lot to Anita Borg and David Wall, and the rest of DEC's Western Research Laboratory. They developed the trace-gathering system that I needed to get the quantitative (i.e. trace-driven simulation) results for this dissertation. I am grateful to Joel Bartlett, Renato De Leone, Jeremy Dion, Norm Jouppi, Bob Mayo, and Don Stark for providing traceable applications. Paul Vixie and Colleen Hawk also helped store the traces. Mike Litzkow and Miron Livny were a great help in adapting Condor to the requirements of these simulations. Paul Beebe and the Systems Lab were able to satisfy the *enormous* computing needs of this dissertation.

I thank many others for their useful feedback. David Wood made numerous useful comments. He was closely involved with the trace-sampling work. Guri Sohi made many critical comments that greatly improved this dissertation. I also wish to thank Jim Goodman and Parameswaran Ramanathan for serving on my committee. Special thanks to Harold Stone for his useful comments on the research in this dissertation.

Last, but not least, I am grateful to my brothers, sisters, and parents for helping me keep things in proper perspective. Finally, I will be forever grateful to Lisa Snow, both for helping to find errors, and for just being there.

# **Table of Contents**

| Chapter 1. Introduction                                     | 1        |

|-------------------------------------------------------------|----------|

| 1.1. Dissertation Overview and Contributions                | 2        |

| Chapter 2. Background and Cache Performance Analysis        | 5        |

| 2.1. Introduction                                           | 5        |

| 2.2. Virtual Memory Concepts                                | 5        |

| 2.3. Set-Associative CPU Cache Concepts                     | 6        |

| 2.4. Previous Cache Analysis                                | 9        |

| 2.4.1. Hardware Monitoring                                  | 9        |

| 2.4.2. Analytical Modeling                                  | 10       |

| 2.4.3. Trace-Driven Simulation                              | 10       |

| 2.4.3.1. Gathering Address Traces                           | 11       |

| 2.4.3.2. Cache Analysis Using Address Traces                | 13       |

| 2.5. Cache Performance Metrics                              |          |

| 2.6. Statistical Techniques                                 | 17       |

| 2.7. The Trace-Driven Simulation Environment                |          |

| 2.8. Conclusions                                            | 20       |

| 3.1. Introduction                                           | 23<br>23 |

| 3.2.2. Storing Long Traces                                  |          |

| 3.3. A Description of the Workloads                         | 30       |

| 3.4. Simulation Results from the Traces                     | 30       |

| 3.4.1. Instruction Mix and Memory Usage                     | 30       |

| 3.4.2. The Multiprogrammed Traces                           | 33       |

| 3.4.3. Miss Frequencies in Multi-Level Cache Configurations | 35       |

| 3.4.4. Secondary Cache Inter-Miss Distributions             | 39       |

| 3.5. The Advantages of Long Traces                          | . 44     |

| 3.5.1. Capturing More Workload Behavior                     |          |

| 3.5.2. Overcoming Cache Initialization                      | . 48     |

| 3.6. Conclusions                                            | . 54     |

| Chapter 4. Trace-Sampling Techniques                        | . 50     |

| 4.1. Introduction                                           | . 50     |

| 4.1. Introduction                                           |          |

| 4.2.1. Obtaining Unbiased Estimators from Set Samples       |          |

| 4.2.1. Constructing the Set Sample                          |          |

|                                                                      | <b>/1</b> |

|----------------------------------------------------------------------|-----------|

| 4.2.1.2. Estimating MPI With a Set Sample                            | 61        |

| 4.2.2. What Fraction of the Full Trace is Needed?                    | 62        |

| 4.2.3. Advantages and Disadvantages of Set Sampling                  | 69        |

| 4.3. Time Sampling                                                   | 69        |

| 4.3.1. Obtaining Unbiased Estimators from Time Samples               | 69        |

| 4.3.2. What Fraction of the Full Trace is Needed?                    | 78        |

| 4.3.3. Advantages and Disadvantages of Time Sampling                 | 86        |

| 4.4. Conclusions                                                     | 87        |

| Chapter 5. Memory System Design With Multi-Megabyte Caches           | 89        |

| 5.1. Introduction                                                    | 89        |

| 5.2. Importance of Multi-Megabyte Caches                             | 90        |

| 5.3. Importance of the CPU Cache Hierarchy                           | 91        |

| 5.4. The Primary Caches                                              | 93        |

| 5.5. Secondary Cache Size Choice                                     | 95        |

| 5.5.1. Effect of Processor-Main Memory Speed Gap                     | 95        |

| 5.5.2. The Effect of Workload Choice                                 | 96        |

| 5.5.3. Effect of Speed Degradation With Larger Caches                | 97        |

| 5.6. Secondary Cache Associativity Alternatives                      | 99        |

| 5.6.1. The Usefulness of Associativity                               | 100       |

| 5.6.2. Replacement Policy Effects                                    | 400       |

| 5.6.3. Effect of Speed Degradation With Associativity                |           |

| 5.6.4. Inexpensive Associativity Implementations                     | 106       |

| 5.7. Secondary Cache Block Size Alternatives                         |           |

| 5.8. Inclusion Design Alternatives                                   |           |

| 5.9. Conclusions.                                                    |           |

|                                                                      |           |

| Chapter 6. Page Placement Algorithms for Real-Indexed Caches         | 120       |

| 6.1. Introduction                                                    |           |

| 6.1.1. Previous Work                                                 |           |

| 6.1.2. Contributions of this Chapter                                 |           |

| 6.2. Motivation for Careful Page Mapping                             | 124       |

| 6.2.1. Page Placement in Cache Bins                                  | 123       |

| 6.2.2. A Simple Static Page Conflict Analysis                        | 124       |

| 6.3. Careful Mapping Implementations                                 |           |

| 6.3.1. Page Coloring                                                 |           |

| 6.3.2. Bin Hopping                                                   |           |

| 6.3.3. Best Bin                                                      |           |

| 6.3.4. Hierarchical                                                  | . 134     |

| 6.4. Trace-Driven Simulation Performance Analysis                    |           |

| 6.4.1. The Simulator                                                 |           |

| 6.4.2. Results                                                       |           |

| 6.4.2.1. The Usefulness of Careful Page Mapping                      |           |

| 6.4.2.2. Static Page Conflict Minimization                           | . 145     |

| 6.4.2.3. Careful Mapping Alternatives                                | . 147     |

| 6.4.2.4. Does PID-Hashed Virtual-Indexing Approximate Real-Indexing? | . 148     |

| 6.4.2.5. Page Size Performance Effects        | 150 |

|-----------------------------------------------|-----|

| 6.4.2.6. The Effect of Main Memory Contention | 151 |

| 6.5. Discussion                               | 153 |

| 6.6. Conclusions                              | 154 |

| Chapter 7. Summary and Future Work            | 156 |

| 7.1. Summary                                  | 156 |

| 7.2. Future Work                              | 158 |

| Appendix A.                                   | 160 |

| Appendix B.                                   | 164 |

| Bibliography                                  | 168 |

|  |  | magnetimagnimagnimagnimagnimagnimagnimagnimagn |

|--|--|------------------------------------------------|

|  |  |                                                |

|  |  |                                                |

# List of Figures

| Chapter 1.                                                           |          |

|----------------------------------------------------------------------|----------|

| 1.1. Hierarchical Memory System Evolution                            | 3        |

| Chapter 2.                                                           |          |

| 2.1. Virtual to Real Address Translation                             | 7        |

| 2.2. Set-Associative CPU Cache Indexing                              | 9        |

| 2.3. Trace-Driven Simulation                                         | 11       |

| 2.4. Cache Performance Metrics                                       | 15       |

| 2.5. Simulation of Homogeneous Hierarchical Configurations           | 19       |

| 2.6. Parallel Simulation with Condor                                 | 20       |

| Chapter 3.                                                           |          |

| 3.1. Code Expansion For Tracing                                      | 24       |

| 3.2. Concatenating Multiple Trace Buffers                            | 25       |

| 3.3. The Phases of Trace Compression                                 | 26       |

| 3.4. Basic Block Compression Code                                    | 27       |

| 3.5. Basic Block Decompression Code                                  | 28       |

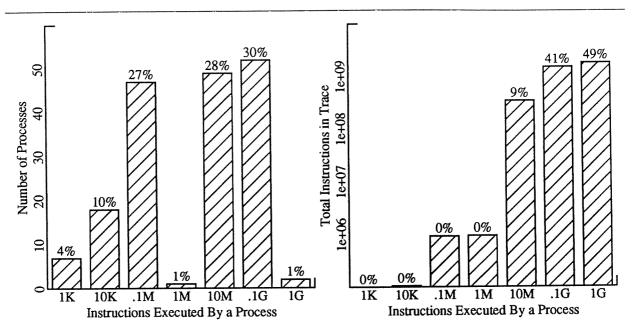

| 3.6. Mult2.2 Processes Classified by Execution Length                | 35       |

| 3.7. Mult2.2 Processes Classified by Memory Usage                    | 36       |

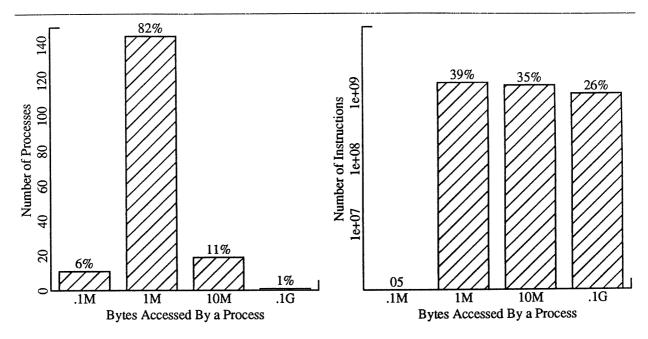

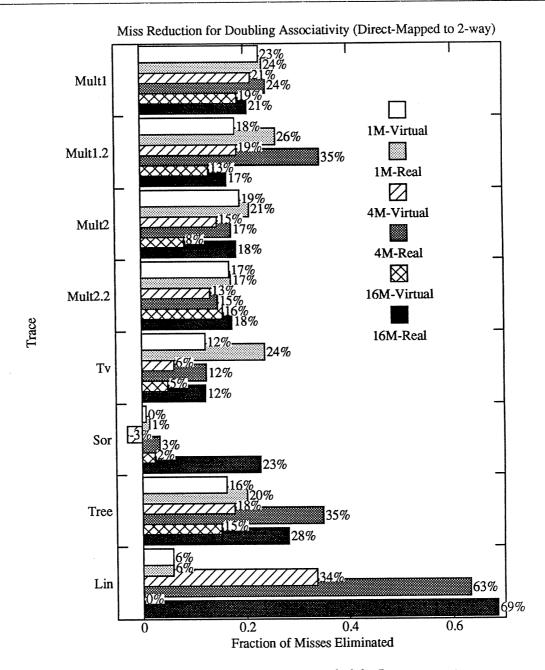

| 3.8. Miss Reduction for Doubling Associativity                       | 40       |

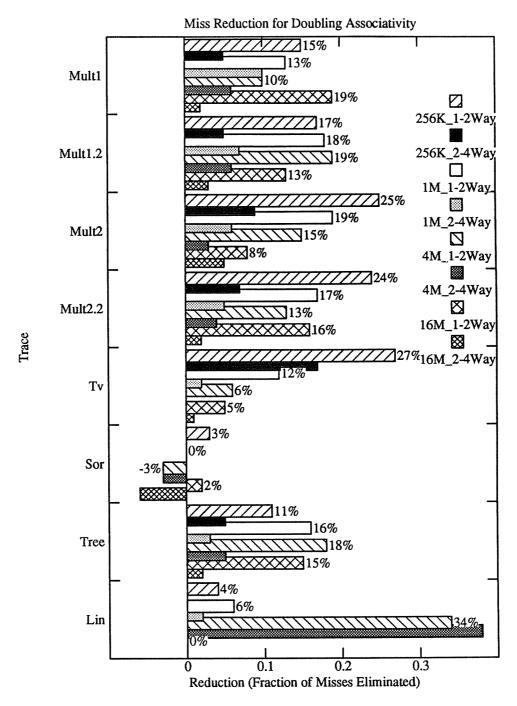

| 3.9. Miss Reduction for Doubling Size                                | 41<br>42 |

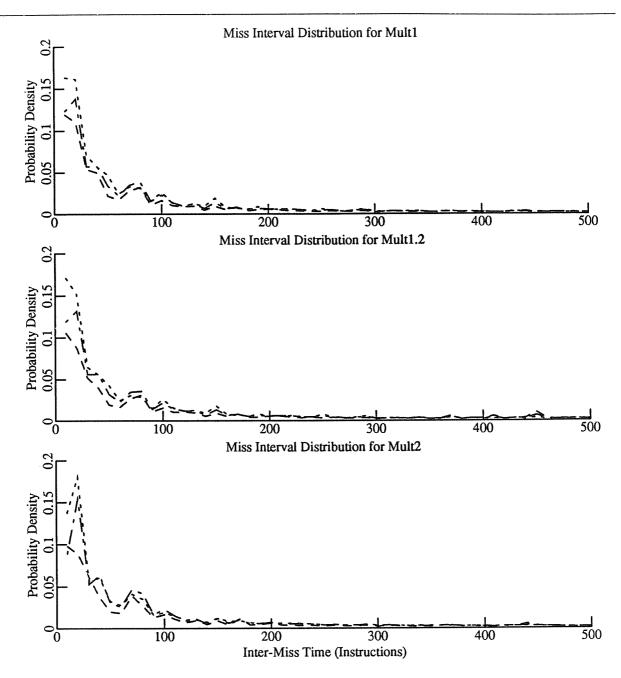

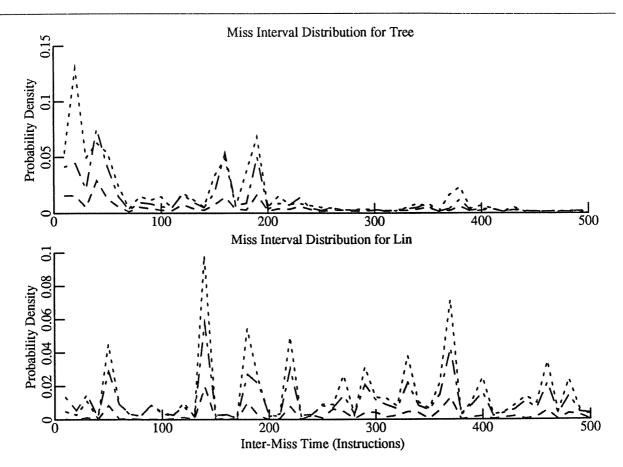

| 3.10a. Inter-Miss Density of Mult1, Mult1.2, and Mult2               |          |

| 3.10b. Inter-Miss Density of Mult2.2, Tv, and Sor                    | 43<br>44 |

| 3.10c. Inter-Miss Density of Tree and Lin                            | 46       |

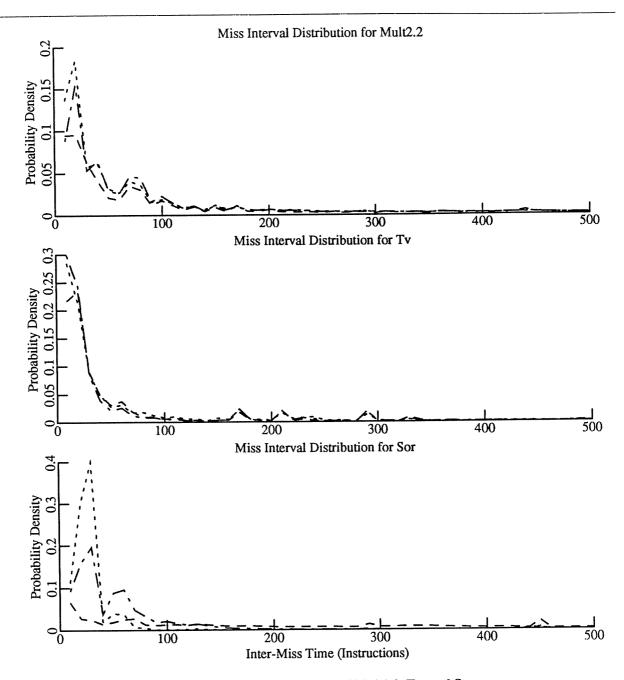

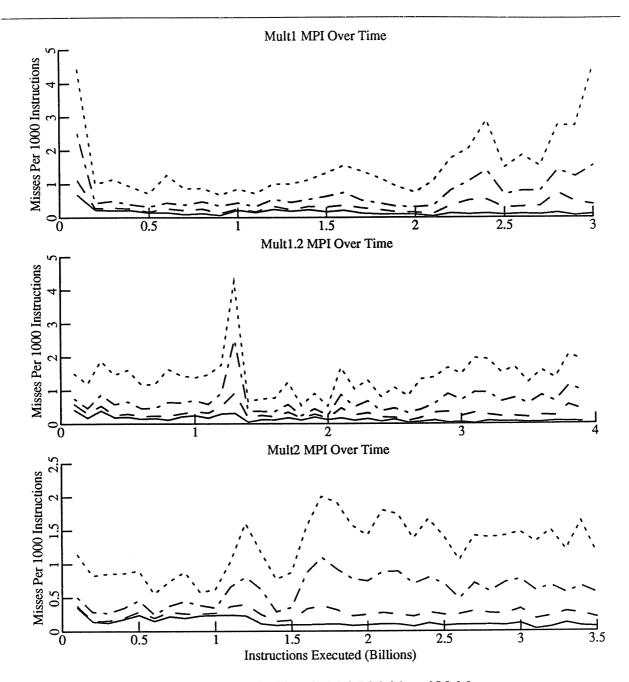

| 3.11a. Variability of Mult1, Mult1.2, and Mult2                      | 47       |

| 3.11b. Variability of Mult2.2, Tv, and Sor                           | 48       |

| 3.11c. Variability of Tree and Lin                                   | 49       |

| 3.12. Fraction of Misses that are Compulsory                         | 52       |

| 3.13. Cumulative Initialization References for Beginning of Mult1.2  | 53       |

| Chapter 4.                                                           |          |

| 4.1. Sampling as Vertical and Horizontal Time-Space Slices           | 57       |

| 4.2. Set Sampling on the Mult1.2 Trace                               | 63       |

| 4.3. Distribution of Set Samples from the Mult1.2 Trace              | 64       |

| 4.4. Range of Performance With Set-Samples                           | 67       |

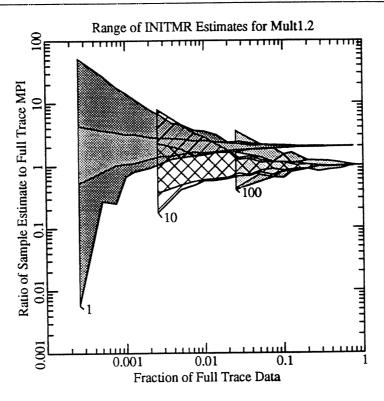

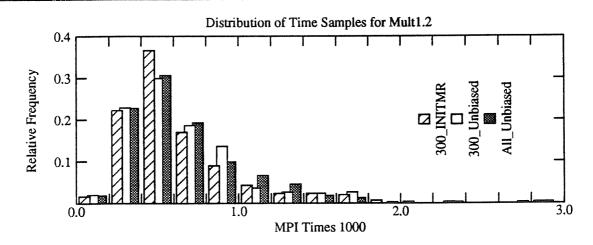

| 4.5. Accuracy of Time Sampling with Mult1.2                          | 80       |

| 4.6a. Accuracy of Time Sampling with Mult1, Mult2, Mult2.2, and Tree | 82       |

| 4.6b. Accuracy of Time Sampling with Tv, Sor, and Lin                | 83       |

| 4.7. Accuracy of Time Sampling for Different Cache Sizes          | 84  |

|-------------------------------------------------------------------|-----|

| 4.8. Range of Time-Sampling Estimate for Mult1.2                  | 85  |

| 4.9. Time-Sample Distributions                                    | 86  |

| Chapter 5.                                                        |     |

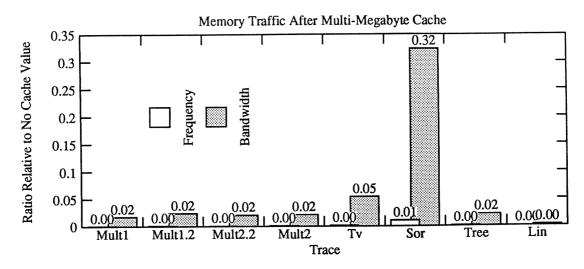

| 5.1. Memory Traffic Reduction With Multi-Megabyte Cache           | 91  |

| 5.2. The Simulated Cache Configuration                            | 92  |

| 5.3. Portions of SCPI for Mult1.2                                 | 94  |

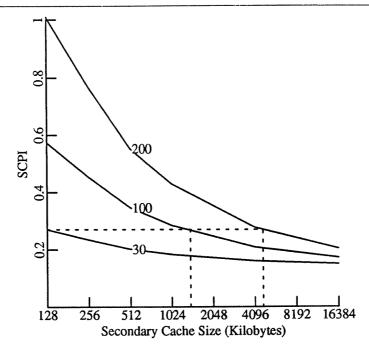

| 5.4. Effect of Miss Penalty on SCPI for Mult1.2                   | 96  |

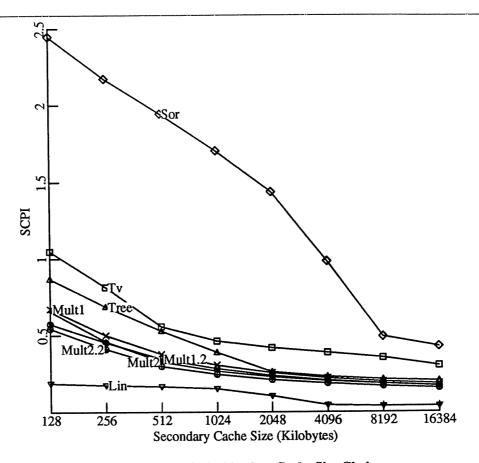

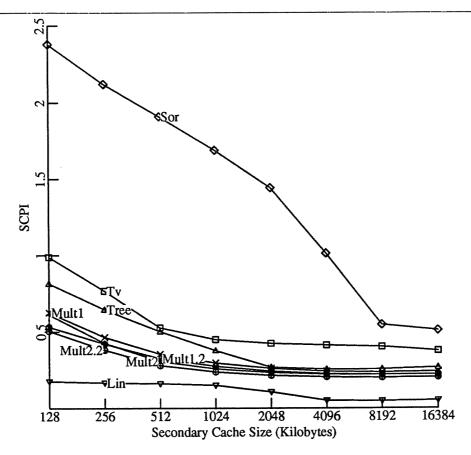

| 5.5. Effect of Workload on Cache Size Choice                      | 97  |

| 5.6. Effect of 10% Speed Degradation Per Cache Size Doubling      | 98  |

| 5.7. Break-Even Access Time Penalties for Cache Size Doubling     | 100 |

| 5.8. Performance Over a Range of Associativities                  | 101 |

| 5.9. Associativity Performance With 10% Speed Degradation         | 105 |

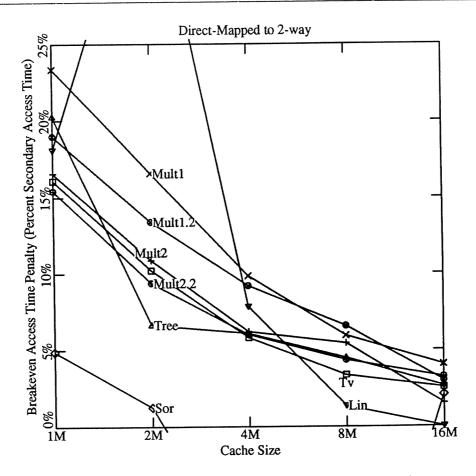

| 5.10a. Direct-Mapped to 2-Way Break-Even Implementation Penalties | 106 |

| 5.10b. Direct-Mapped to 2-Way Break-Even (Blow-up)                | 107 |

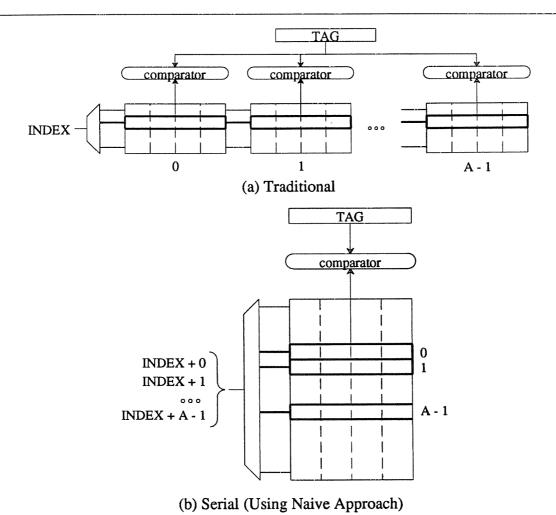

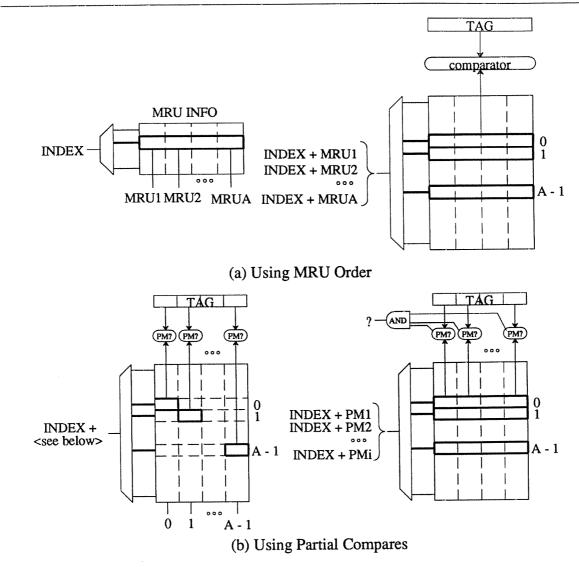

| 5.11. Implementing Set-Associativity                              | 108 |

| 5.12. Improved Implementations of Serial Set-Associativity        | 109 |

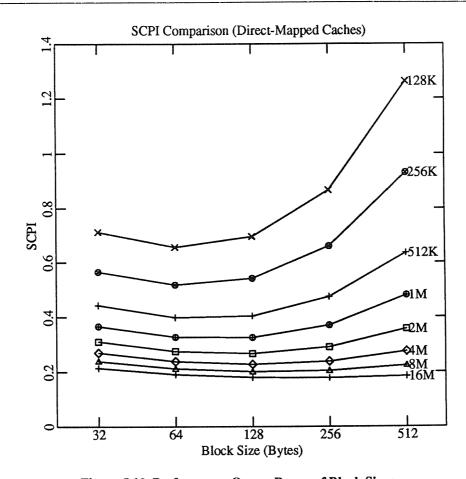

| 5.13. Performance Over a Range of Block Sizes                     | 114 |

| Chapter 6.                                                        |     |

| 6.1. Virtual Memory and Set Indexing Interaction                  | 121 |

| 6.2. A Virtual-Indexed Bin Placement                              | 123 |

| 6.3. Random and Careful Real-Indexed Bin Placements               | 125 |

| 6.4. Cache Placement Conflicts                                    | 127 |

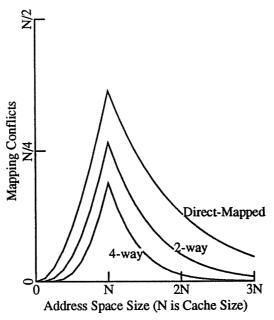

| 6.5. Random Mapping Conflicts                                     | 128 |

| 6.6. Bin Choice Code for Page Coloring                            | 130 |

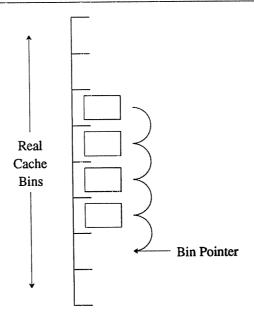

| 6.7. Page Placement By Bin Hopping                                | 131 |

| 6.8. Bin Choice Code for Bin Hopping                              | 132 |

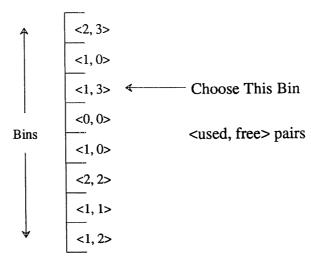

| 6.9. Code to Choose Among Bins                                    | 133 |

| 6.10. Bin Choice Code for Best Bin                                | 133 |

| 6.11. Page Placement by Best Bin                                  | 134 |

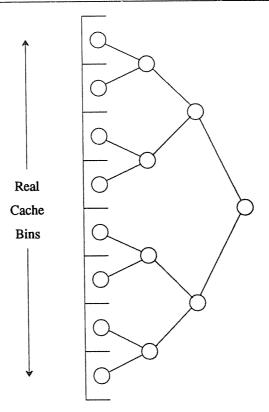

| 6.12. Page Placement Using Hierarchy                              | 136 |

| 6.13. Bin Tree Traversal                                          | 135 |

| 6.14. Mapping Tree Nodes to Bins                                  | 137 |

| 6.15. Bin Choice Code for Hierarchical                            | 138 |

| 6.16. LRU List Implementation With Available Page Frames          | 139 |

| 6.17. Mult2.2 Results for Different Page Mappings                 | 141 |

| 6.18. Direct-Mapped Hierarchical Miss Reductions for All Traces   | 142 |

| 6.19. Mult2.2 Careful Mapping Improvement                         | 144 |

| 6.20. Mult1.2 Results for Different Page Mappings                 | 144 |

| 6.21. Conflicts for Mult2.2                                       | 146 |

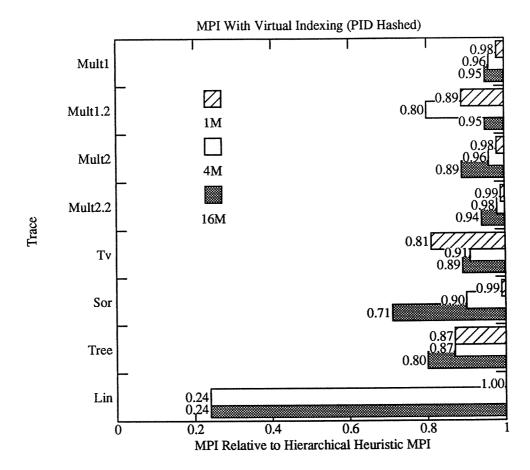

| 6.22. Hierarchical Reduction vs. Conflicts Eliminated             |     |

| 6.23. Virtual and Real Indexing Comparison                        |     |

| 6.24. Virtual and Real Indexing Associativity Improvement         | 151 |

# List of Tables

| Chapter 3.                                                           |     |

|----------------------------------------------------------------------|-----|

| 3.1. The Types of Preprocessed Trace Entries                         | 29  |

| 3.2. A Description of the Traced Programs                            | 31  |

| 3.3. A Description of the Studied Workloads                          | 32  |

| 3.4. Instruction Information on the Traces                           | 33  |

| 3.5. Memory Requirements of Traces                                   | 33  |

| 3.6. Process Statistics of Multiprogrammed Traces                    | 34  |

| 3.7. Primary Cache MPI                                               | 36  |

| 3.8. Secondary Cache MPI                                             | 38  |

| 3.9. Instructions to Fill Primary Caches                             | 49  |

| 3.10. Instructions to Fill Direct-Mapped Secondary Caches            | 50  |

| 3.11. Instructions to Fill 4-way Secondary Caches                    | 51  |

| 3.12. Instructions to Warm Cache to Knee                             | 52  |

| 3.13. Trace Length for Five Misses Per Block Frame                   | 54  |

| Chapter 4.                                                           |     |

| 4.1. Errors of Different Set-Sample MPI Estimates                    | 62  |

| 4.2. Set Sampling Coefficients of Variation for Direct Mapped        | 65  |

| 4.3. Set Sampling Coefficients of Variation for 2-Way                | 66  |

| 4.4. Set-Sampling Error Prediction                                   | 68  |

| 4.5. Accuracy of Cold-Start Techniques for Mult1.2                   | 72  |

| 4.6. Accuracy of Cold-Start Techniques With Direct-Mapped Caches     | 73  |

| 4.7. Accuracy of Cold-Start Techniques With 4-Way Set-Associativity  | 74  |

| 4.8. Scoring of Different Cold-Start Techniques                      | 75  |

| 4.9. $\mu$ and the Accuracy of its Estimator ( $\hat{\mu}_{split}$ ) | 76  |

| 4.10. Accuracy of INITMR Time-Sample MPI Estimates                   | 77  |

| 4.11. Individual Versus Merged $\hat{\mu}_{split}$ Estimation        | 79  |

| Chapter 5.                                                           |     |

| 5.1. Primary Cache Performance                                       | 94  |

| 5.2. Effects of Associativity on Cache Performance                   | 102 |

| 5.3. Improvement of Replacement Policies                             | 104 |

| 5.4. Expected Probes of Associativity Implementations                | 110 |

| 5.5. Read Probes of Inexpensive Associativity Implementations        | 111 |

| 5.6. Block Size Alternatives                                         | 115 |

| 5.7. Implicit and Explicit Inclusion Invalidate Frequency            | 117 |

| Chapter 6.                                                           |     |

| 6.2. Careful Mapping Comparison                  | 148 |

|--------------------------------------------------|-----|

| 6.3. Performance of Mapping Schemes for Mult2.2  |     |

| 6.4. Cache Misses vs. Page Size                  |     |

| 6.5. Memory Referenced vs. Page Size             |     |

| 6.7. Cache and Page Misses for Memory Contention |     |

# **List of Definitions**

| Chapter 2.                                   |          |

|----------------------------------------------|----------|

| 2.1. Definitions for Virtual Memory          | 5<br>7   |

| Chapter 4.                                   |          |

| 4.1. Set Sample                              | 59<br>59 |

| Appendix A.                                  |          |

| A.1. Page Mapping Function                   | 160      |

| A.2. Page Frame and Cache Bin Correspondence | 160      |

| A.3. Cache Size Independent Mapping Function | 161      |

| A A Rit Payared Rin Tree                     | 16       |

# **List of Theorems**

| Chapter 4.                                       |            |

|--------------------------------------------------|------------|

| 4.1. When a Constant-Bits Sample is a Set Sample | 59         |

| Appendix A.                                      |            |

| A.1. Value of BRBT Node                          | 161<br>162 |

# Chapter 1

# Introduction

The memory system is a critical component of any high-performance computer system. Memory speed is often a major component of the perceived execution speed of the computer since the processor can only execute as fast as the memory system provides data. Computer users would prefer a memory that is both infinitely large and infinitely fast, or at least one that is large enough and fast enough. The challenge is to design a cost-effective memory system that meets these goals.

Rapid technology change always alters the memory system design problem, making previous designs an insufficient solution, and new research essential. Memory densities are dramatically improving: main memories of hundreds of megabytes will be common in the future. Processors are getting faster: processors will execute hundreds of millions of instructions in a single second. With more processing and memory capabilities, users solve different and larger problems than previously envisioned. These technology and usage changes reshape the problems presented to the memory system designer. As memory systems evolve, design decisions must be constantly reevaluated.

This dissertation analyzes a memory system that is motivated by increasing processing speeds and expanding main memories. While main memories are getting much larger, they are not getting much faster. This creates a speed gap between the processor and main memory. The processor can perform hundreds of operations in the time it takes to service a single main memory request, so memory accesses must be rare. With this large speed gap, it becomes particularly difficult to meet the expectations of the user: a fast and large memory. While a given memory may be large enough, it is probably not fast enough.

The problem is that larger memories are inherently slower than smaller memories because of physical limitations. Given this problem, it may at first seem impossible to build a memory system that has both a large capacity and a high speed. Fortunately, there is an elegant design solution that overcomes these physical limitations. A smaller (faster) and a larger (slower) memory are configured

hierarchically, yet they appear as a single memory because the faster memory transparently caches the frequently-referenced contents of the slower memory. The average speed of the hierarchy is nearly the speed of the fastest memory because it services most references (locality of reference [DENN68]). The largest memory decides the capacity of the hierarchy because it services all the other references that the smaller one(s) cannot. At no burden to the programmer, hierarchical memory systems bridge the large speed gap between processing and memory by simultaneously using the speed and capacity advantages of small and large memories.

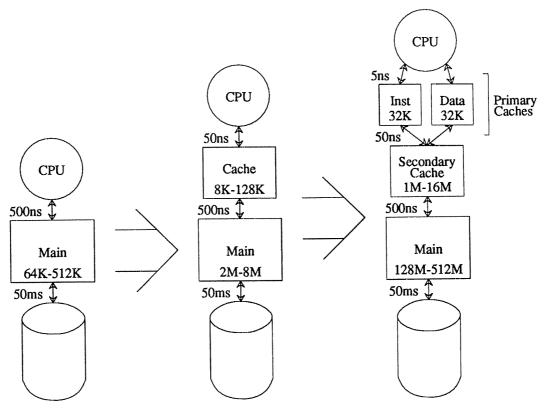

Figure 1.1 shows the evolution (from left to right) of hierarchical memory systems to fill the processor-memory speed gap. Technology changes push designs to the far right of the figure: to the memory system examined in this study. *Virtual memory* (on the far left) is the earliest transparent hierarchical structuring of mechanical (disk or drum) and electronic main memories [FOTH61, KILB62, KIEL82]. Main memory could successfully bridge the speed gap between processors and mechanical storage when it could service references at the speed of the processor. Faster processors create another speed gap since large main memories cannot equal processor speeds. Another hierarchy level bridges this gap: *cache* memory. Caches are essential for the processor-main-memory performance gap just like virtual memory is essential for the main memory and disk gap. Caches are faster (but smaller) than main memories, so they can satisfy processor references more quickly. Caches greatly improve memory system performance, at no burden to the programmer.

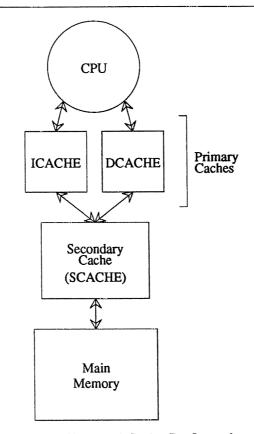

With even faster processors, a single cache becomes an insufficient buffer between the processor and main memory. A two-level cache configuration is necessary. Again, an addition of another level to the hierarchy allows the capacity advantages of the large cache to be combined with the speed advantages of the smaller cache. The large cache reduces the frequency of main memory accesses, which is essential because they take so long, but a large cache is too slow to directly service the processor. This leads to the configuration on the far right of Figure 1.1, one with smaller primary and larger secondary CPU caches. This two-level cache configuration gracefully tolerates a processor-memory speed gap of even a hundred or more. The primary caches service most processor references, and the secondary cache services most of the references that escape the primary caches. Split primary caches provide high bandwidth to the processor; separate instruction and data caches allow instruction and data references to be serviced simultaneously.

The technology changes that drive hierarchical memory systems to two cache levels are evident in Figure 1.1. Microprocessor speeds have improved by a factor of one hundred over the last decade while main memory speeds have improved by only 50% in the same period. CPU caches fill this speed gap by pushing the processor up in the hierarchy. Memory sizes have grown by several orders of magnitude. Caches also grow with each evolutionary generation. These large caches can satisfy most of the references from even the largest workloads.

#### 1.1. Dissertation Overview and Contributions

This study focuses on the evaluation and design of the evolutionary two-level cache configuration depicted on the far right in Figure 1.1. In particular, this dissertation concentrates on large secondary caches. Most previous cache analyses focus on smaller primary caches because only recent technology advances and increasing workload sizes necessitate the larger caches as a part of a two-level cache configuration. Evolutionary trends suggest that these caches will be multiple megabytes, an order of magnitude larger than the previous generation of caches. The scope of this study is restricted to

Figure 1.1. Hierarchical Memory System Evolution.

This figure shows the evolution of hierarchical memory systems (from left to right) to fill the gap between processor and memory speeds. At the top of the hierarchy is the processor (CPU), and at the bottom is non-volatile (mechanical) storage. In the middle, there are several levels of memory, both cache and main, with sizes given. The latency required for a transfer between levels is also given. The latencies and sizes depicted are only examples. This dissertation studies secondary caches in a configuration like the one at the far right.

uniprocessors because they continue to push the limits of low-cost computational performance, though multi-megabyte secondary caches are equally or more useful for multiprocessors.

While primary cache and main memory design considerations are much the same as in the previous generation, the new secondary caches are fundamentally different. Secondary caches are different from primary ones for two reasons. First, secondary caches will be as large as main memories once were, much larger than previous (or future) primary caches. Second, primary caches directly service processor references, while secondary caches service only the references not satisfied by the primary caches. Most previous research has focused on primary cache design. This dissertation studies the secondary cache, which sees memory references with very different characteristics.

Although they are of similar size, multi-megabyte secondary caches are fundamentally different from previous main memories. One difference is the time to access the next hierarchy level: disk accesses take many orders of magnitude longer than main memory accesses. This latency difference makes secondary cache design very different. Secondary caches can use the main memory much more frequently than previous main memories could access the slow disk.

The differences in multi-megabyte secondary cache design motivate the research in this dissertation. The first component of this research involved gathering tools appropriate for analyzing multi-

megabyte secondary caches. As memory systems evolve, the tools used to evaluate them also must evolve. This dissertation describes the implementation and use of new cache performance analysis tools. By evaluating multi-megabyte secondary caches in the proper framework, new insights into their behavior and design are evident.

Chapter 2 defines the basic concepts related to virtual memory and CPU caches, and gives the default parameters that are assumed throughout the rest of this dissertation. It also surveys some important previous cache performance analysis studies, and shows trace-driven simulation to be an effective performance analysis tool for cache memories. It introduces the *MPI* and *SCPI* cache performance metrics, and describes the statistical techniques used throughout this dissertation. It then describes a simulation environment that allows trace-driven simulation results to be gathered quickly. Chapter 2 establishes the basis for the rest of the research included in this dissertation.

Chapter 3 then describes the collection of superior traces for the analysis of multi-megabyte caches. These traces predict the workloads that will execute on future high performance processors that have main memories of hundreds of megabytes. The traces are one hundred times longer than previous traces, and are taken from workloads that are ten times larger than previously traced. Chapter 3 further shows the advantages of very long traces for multi-megabyte cache analysis.

The problem with long traces is the enormous computing resources needed to simulate with them. Chapter 4 discusses trace-sampling techniques that use only a portion of the long trace references, and consequently reduce the required simulation time, to get accurate cache performance results. Sampling can reduce simulation time by more than an order of magnitude while introducing only small errors.

Chapter 5 gives more detailed motivation for the two-level hierarchical cache configuration shown in Figure 1.1. It shows that multi-megabyte caches are needed as the processor-memory speed gap reaches a factor of one hundred. It then discusses some key design considerations of multi-megabyte secondary caches: block size, associativity, and multi-level inclusion.

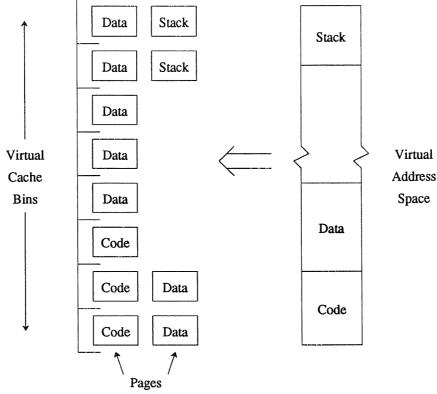

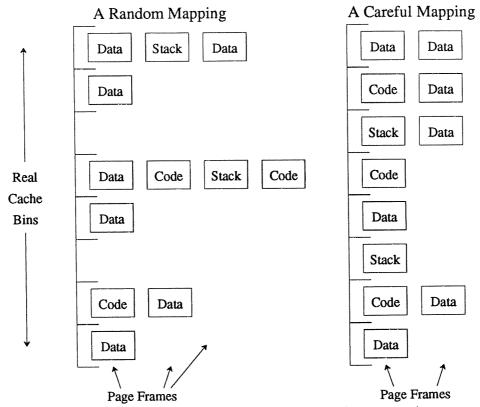

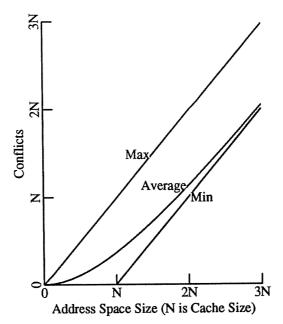

Chapter 6 examines the interaction of virtual memory and set-associative CPU caches. Because of their interaction, the virtual to real page mapping affects the placement of data in the cache. Chapter 6 introduces the problem caused by this interaction: page conflicts. It also introduces a simple model to measure the quality of naive page placement in the cache. This model suggests that 30% of pages may be poorly placed when they are naively mapped to page frames. Chapter 6 introduces and examines practical page mapping techniques that improve the placement of data in the cache and, consequently, improve cache and memory system performance. Trace-driven simulation shows that careful page mapping eliminates 10%-20% of direct-mapped real-indexed cache misses. Thus, careful page mapping can cause a cache to act much larger, at no hardware cost.

Finally, Chapter 7 discusses the conclusions of this research, and areas for future research. This dissertation presents the analysis required to understand the performance and design issues involved with multi-megabyte secondary caches.

# Chapter 2

# Background and Cache Performance Analysis

#### 2.1. Introduction

This chapter gives the memory system background needed for the analysis of the subsequent chapters. In Section 2.1 and Section 2.2, this chapter discusses definitions and default parameters of the virtual memory and cache configurations examined throughout this dissertation. Section 2.3 surveys the most important previous cache performance studies, and motivates the use of trace-driven simulation. Section 2.4 describes the cache performance metrics used throughout this dissertation. Section 2.5 summarizes the statistical techniques used in Chapters 4 and 6. Section 2.6 then describes a simulation environment that takes advantage of levels of homogeneity and parallelism. This chapter discusses the tools used in the subsequent research in Chapters 3, 4, 5, and 6.

## 2.2. Virtual Memory Concepts

This section summarizes key concepts of virtual memory that are used throughout this dissertation. Definition 2.1 gives key definitions and default parameters related to virtual memory.

## Definition 2.1. Definitions for Virtual Memory.

- Page A fixed-size, aligned, and contiguous portion of virtual memory that is managed as a unit. The default page size is 16 kilobytes.

- Page Frame Physical memory that can hold a page. Typically, this refers to main memory. The number of page frames times the page size is the size of the main memory. The default main memory size is 128 megabytes.

- Page Fault An exception that occurs when a referenced page is not held in the main memory. Usually, the operating system stops the user-level program that faulted, loads the page from disk into main memory, and restarts the program.

- Page Mapping (Placement) The relationship between virtual memory pages and page frames. The page mapping specifies where a given page is stored.

- Page Mapping Function (Policy) The algorithm that determines the page mapping.

- Page Replacement The removal of a page from main memory to make room for a new page. This may require writing the replaced page back to disk.

- Page Replacement Policy The algorithm that chooses the page(s) that will be removed from main memory. Replacement policies tend to choose pages that were not recently referenced. The default is to replace the least-recently-used page.

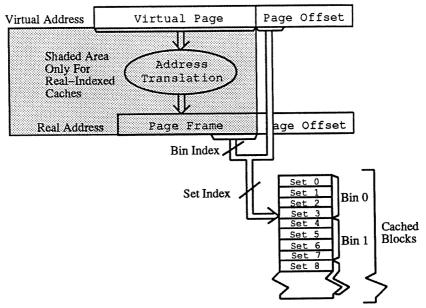

The goal of virtual memory is to provide the user with a unified view of a large and fast memory, although the physical memory is really structured hierarchically. Two separate address spaces provide this view. The user references virtual addresses while real addresses index into the physically available memory. The virtual memory system manages the memory in pages. At any given time, a virtual memory page may either reside in a (physical) main memory page frame or it may be on disk. That is, each page maps to page frames in the main memory or disk memory. When there are no page faults, the system translates each virtual (or page) address to a real (or page frame) address and the main memory is directly accessed. This address translation is depicted in Figure 2.1. Because pages (frames) are properly aligned, the translation does not modify the offset of an address within a page (i.e. the bottom address bits are unchanged). Translation does modify the upper address bits. It determines the page frame corresponding to a virtual page by consulting the page mapping, often a page table. Occasionally, the page table shows that a virtual page is not contained in the main memory. Then, a page fault awakens the system software, and a page rearrangement resolves the fault. Pages may need to be written-back to the disk because of the page fault.

Virtual address translation is typically a fully associative mapping of pages to page frames. This means that any page can be stored in any page frame in main memory. This mapping flexibility allows the system software to choose many different maps of pages to page frames. It also allows considerable flexibility in deciding which pages will reside on the disk and which will be placed in main memory. Typically, recently used pages are held in the main memory, and unreferenced pages reside on the disk. With this policy, the page fault frequency will be low if there is enough locality of reference. The page fault frequency is a key metric of the performance of a virtual memory system. The more often faults occur, the more often the disk must be accessed. Since a disk access is so slow (millions of instructions can be executed during a disk access), page faults must be rare for good performance.

## 2.3. Set-Associative CPU Cache Concepts

This section summarizes key concepts of caches that are used throughout this dissertation. Definition 2.2 gives key definitions and default parameters related to caches.

Figure 2.1. Virtual to Real Address Translation.

This figure shows the translation from virtual addresses to real addresses. The virtual page number translates into a real page frame number.

## **Definition 2.2. Definitions for Caches.**

- Block A fixed-size, aligned, and contiguous portion of memory that is managed as a unit. A block is similar in function, but is typically much smaller than, a virtual memory page. In this dissertation, the primary cache block size is 32 bytes and the secondary cache default block size is 128 bytes.

- Block Frame A cache memory location that can store a block. The size of the cache is the number of block frames times the size of a block. Each primary cache contains 32-kilobytes worth of block frames. The secondary cache size varies from 128-kilobytes to 16-megabytes.

- Set The block frame(s) that can store a block. Each block indexes to a particular set, and only the block frames within that set can hold the block.

- Cache Miss A hardware-handled exception that occurs when the processor references a block that is not in the cache. The cache replaces another block from the same set, and loads the referenced block into the cache to service the reference.

- Associativity The number of block frames in a set, or the number of block frames where any given block can be stored. The primary caches are directmapped (associativity of one) and the associativity of the secondary caches range from one to four.

- Indexing (Placement) The selection of a set using index bits from the address of a reference. If the index bits come from the virtual (real) address, the cache is virtual-indexed (real-indexed). Except for Chapter 6, virtual-indexing is used throughout this dissertation. The virtually-indexed secondary caches use process-identifier (PID) hashing so that common virtual addresses do not index to the same set 1. Virtual-indexed PID-hashing approximates real-indexing. Note that all the virtually-indexed caches used in this dissertation are tagged with PIDs, and that the cache entries are not flushed at process switches.

<sup>1.</sup> For each address space (or process) an 8-bit PID is exclusive-ored with the upper (virtual) index bits to choose the set.

- Block Replacement Removing a block from the cache to make room for a new block. In a write-back cache, this may require writing the replaced block into main memory.

- Block Replacement Policy The algorithm that chooses the block that will be replaced when space must be allocated. The default is a random block from the set.

- Write Policy Decides when writes propagate to the next level in the hierarchy. Write-through implies that updates immediately propagate when any write occurs. Write-back implies that updates occur at block replacement. Write-back is assumed in this dissertation<sup>2</sup>.

- Multi-Level Inclusion The property that the contents of a cache closer to the processor must always be contained in a cache further from the processor [BAEW88]. It is particularly useful when maintaining coherency in a shared memory multiprocessor or in the presence of I/O devices. Inclusion is not maintained between the primary and secondary caches in this dissertation, except in Section 5.8. Inclusion between the CPU caches and the main memory is maintained in Chapter 6.

The function of a CPU cache is similar to virtual memory: the cache holds a dynamic portion of the blocks that service most memory references. The design of caches is considerably different from the design of virtual memory, however. Hardware manages caches while software manages virtual memory misses. The major reason for this is, as suggested in Figure 1.1, that the time for a CPU cache miss is much less than the time for a page fault. Software intervention is useful and affordable when a page fault costs millions of instructions. Software intervention is too slow for cache misses, so hardware must service them as quickly as possible. A cache is set-associative rather than fully associative. This means that each cache block indexes to a set, and the block can only be stored in the few block frames in that set. Hardware set-associativity implementations allow very fast associative access to blocks stored in the cache.

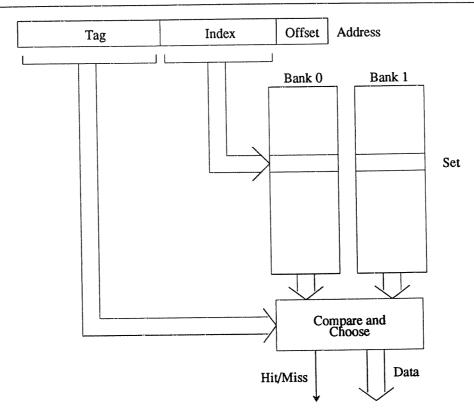

Figure 2.2 shows the operation of a 2-way set-associative cache. The bottom bits of the address are the offset within a block, much like the page offset. Set-associativity, unlike full page associativity, extracts index bits from the address to choose the set where the block will reside. The index bits are typically in the middle of the address. The cache compares the upper tag bits of the address against other tags in the set. When the cache holds a block, its tag is stored for later comparison. When the tag bits of the address match a stored tag, the block is in the cache (a hit). When a referenced block is not found in the cache (a miss), it replaces another block in its set so that later references will find the block (later references will hit).

Figure 2.2 depicts a two-way set-associative cache because there are two cache memory banks. This dissertation also examines associativities of one and four. With 1-way, or direct-mapped, there is only a single bank, meaning that each block can only reside in a single cache block frame. Direct-mapped is the opposite end of the associativity spectrum from the full associativity of virtual memory. A 2-way or 4-way set-associative cache has more mapping flexibility than a direct-mapped cache

<sup>2.</sup> Additionally, the cache is write-allocate, meaning that on write misses, the new block is loaded and then immediately updated in the cache.

Figure 2.2. Set-Associative CPU Cache Indexing.

This figure shows the operation of a 2-way set-associative cache. The index bits choose the set. The associative matching hardware decides if the cache contains the block referenced by the address.

because there are more frames where a given block can reside. On the other hand, a direct-mapped cache can be faster than caches of higher associativity since its design is simpler.

As with virtual memory page faults, cache misses tend to occur infrequently because of locality of reference. The more often there are misses, the more often the next slower memory in the hierarchy must be accessed. Misses must be sufficiently rare so that their performance degradation is not too high. The cache miss frequency is a key cache performance metric that is estimated throughout this dissertation.

## 2.4. Previous Cache Analysis

This section surveys many previous cache performance studies. It discusses hardware monitoring and analytical models, and shows that trace-driven simulation is a powerful tool for the performance analysis of cache memories.

## 2.4.1. Hardware Monitoring

The most precise way to measure cache performance is to take direct measurements by monitoring the operation of a cache. This often involves measurement hardware designed specifically for a given system. For example, Clark, et al., discuss microcode histogram hardware for the VAX 11/780 and 8800 [CLAR83, CLAE85, CLBK88]. The histogram counts determine many cache performance metrics, including cache miss frequencies, misses per instruction, and cycle time effects on the average

instruction. Wood describes the embedded SPUR monitoring hardware, which also measures many cache performance metrics, but is an internal part of the SPUR cache design [WOOD90], rather than a plug-in measurement device.

Hardware monitors give the most accurate cache performance results, but they are costly and can only measure existing cache configurations. It is extremely useful to test a range of cache configurations since trends and fundamental cache performance factors can be determined. Hardware monitoring may not be a cost-effective alternative for the analysis of a wide range of configurations.

## 2.4.2. Analytical Modeling

Analytical modeling is much less costly than hardware performance monitoring, and is flexible enough to estimate performance over a wide range of configurations. Strecker shows that simple equations can predict cache miss ratios with different process switching [STRE83]. Haikala estimates cache performance with process switching using a Markov Chain model, given the LRU stack distribution [HAIK84]. Smith and Goodman use a loop reference model to predict instruction cache performance and show that set-associativity can be better that full associativity [SMIG85]. Thiebaut and Stone develop analytical techniques to estimate the cache footprint left by an executing process for use in predicting cache performance with process switching [THIS87]. Voldman, et al., [VOMH83] and Thiebaut [THIE88, THIE89] show that fractal analysis can predict cache performance. Agarwal, et al., develop a model that counts start-up, non-stationary, and interference effects on cache performance estimates [AGHH89]. Singh, et al., use empirical curve-fitting to predict cache performance [SIST88]. Higbie develops a cache performance model based on rules-of-thumb [HIGB90].

The problem with these models is that it is difficult to establish confidence in their results without direct comparison to more accurate results. Analytical models are most useful when they increase understanding and intuition. For example, simple rules-of-thumb such as "The miss rate of a direct-mapped cache of size X is about the same as a 2-way set-associative cache of size X/2" [HENP90] or "Doubling the cache size decreases the miss rate by 25%" [HIGB90] are good first-cut approximations, even if they are not always correct. Analytical models may not be appropriate when accuracy is required, but they are useful when more accurate workload models are not available or when simulation time is not affordable.

#### 2.4.3. Trace-Driven Simulation

This dissertation uses trace-driven simulation for cache analysis because simulation overcomes the limitations of hardware monitors and analytical models. Trace-driven simulation uses memory reference traces to model cache behavior. Unlike hardware monitors, a wide range of cache configurations can be cost-effectively examined with trace-driven simulation. Unlike analytical models, simulation produces accurate results, at least to the limits of the available traces. Hundreds of previous cache performance studies have used trace-driven simulation, including Smith's excellent survey [SMIT82]. In the process, it has been established as powerful tool for cache performance evaluation.

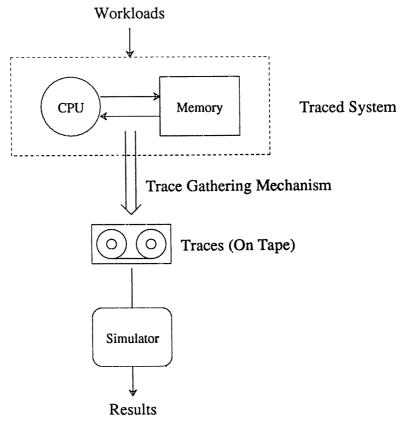

Figure 2.3 depicts the production of trace-driven simulation cache performance results. The idea is to capture the processor-memory references under realistic conditions, then feed the references into a cache simulator. The first, and most important, phase in the process is gathering the trace data from a given workload. This is done by the trace-gathering mechanism, a component of the traced system.

The trace data describes the memory reference behavior of the processor, and may be stored for later use. The simulators of the second phase recreate the memory references using the trace data.

Figure 2.3. Trace-Driven Simulation.

This figure shows the major components of any trace-driven simulation study.

The second phase of trace-driven simulation is the generation of simulation results using the previously captured trace data. Note that while the trace data is gathered only once, it can be used often. The simulator interprets the trace data and gives cache performance results for desired cache configurations. It extracts each reference from the trace and submits them to the simulated cache, just as the real references are submitted to the real cache. The simulator steps through the actions that the cache the cache would execute, so the cache performance estimate of the simulator is an accurate indicator of cache performance for the traced workload. By varying the simulated cache configuration, the simulator can capture the performance of many caches.

The next two subsections describe previous work related to the trace gathering and usage phases of trace-driven simulation.

### 2.4.3.1. Gathering Address Traces

It is unfortunate that the most important component of any trace-driven simulation study, the traces themself, receive so little attention in the literature. Any trace-driven simulation is only as good as the traces; it is important to gather traces that properly characterize the workloads of the simulated machine. Although all sequences of memory references tend to exhibit locality of reference, the exact memory reference behavior contained in a trace has a large effect on cache performance. Clark, et. al.,

show that trace-driven simulation performance estimates can be optimistic because complete memory reference behavior is not available in the traces [CLAE85]. Smith warns that trace-driven simulation results vary greatly for different architectures and workloads [SMIT85]. It is useful to obtain traces from a variety of workloads to determine their differences and cache performance effects.

Many traces have been gathered by either simulating architectural behavior or stepping through the execution of a program using operating system facilities to control the execution of a program. Entries are written into the trace at each execution step, corresponding to program execution. The simplicity of these techniques is useful, but it is time-consuming to gather these traces, and may be difficult to include operating system or multiprogramming references. Agarwal, et al., argue that hardware microcode modifications can be an effective mechanism to gather traces that include all references, user and operating system [AGSH86, AGAR87, AGHH88]. Altered microcode writes out trace entries for each executed instruction. Since the hardware mechanism requires little software support, operating system references can be traced. Agarwal, et al., show the importance of operating system references to correctly predict cache performance: operating system references are significantly different from user references; they may increase the cache misses in trace-driven simulation by 50% [AGHH88]. While this is an important achievement, the difficulty is that the microcode modifications can be expensive, inflexible, and are only useful for microcoded machines.

Borg, et al., developed an alternative tracing technique that uses code modification to trace programs [BoKL89, BoKW90]. The application code is modified to output trace data at specific points. The main advantage of code modification is that it can be implemented entirely in software, no hardware changes are required. This mechanism gathered the multi-billion-instruction traces described in Chapter 3. Properly interleaved multi-process trace data can be collected by code modification with operating system and compiler support. With the code of the operating system also modified, operating system references can even be gathered. Using similar techniques, Stunkel and Fuchs collect and analyze multicomputer traces [STUF89, STJF91]. Eggers, et al., [EGKK90] describe a tracing scheme that (using compiler data flow analysis) requires fewer trace entries than the two previous schemes, similar to the Abstract Execution of Larus [LARU90]. PFC-Sim also eliminates many entries [CAKP91]. The advantage of fewer trace entries is lower trace storage requirements and less execution time distortion. The disadvantage is that trace data interpretation is more complex.

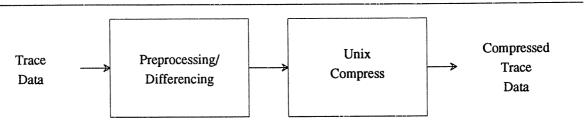

Much trace data storage is required to collect the long traces needed to analyze multi-megabyte caches. Samples introduced an effective compression technique to reduce trace data storage requirements without information loss [SAMP89]. It combines Ziv-Lempel [WELC84] compression with differencing of the trace data, giving dramatic storage space reductions for traces. A variant of this technique, described in Chapter 3, compresses the traces used in this dissertation.

Techniques with information loss can also reduce trace data requirements. Smith's *stack deletion* and *snapshot method* [SMIT77] eliminate much trace information with only small effects on fully-associative simulation results. Stack-deletion eliminates many references to the most-recently-used items, while the snapshot method eliminates many time-contiguous references. The idea is that many most-recently-used or time-contiguous items will hit in the cache anyway, so there is no need to simulate them; all that is needed is a proper estimate of the number of misses in a trace. Puzak's *trace* (*tape*) *stripping* [PUZA85] is stack deletion (restricted to one most-recently-used item) for set-associative caches. References are stripped away by simulating the full trace on a small direct-mapped cache and recording only the misses. Puzak showed that, provided some restrictions are upheld, the stripped trace

produces the same number of set-associative cache misses as the full trace. Wang and Baer subsequently extended trace-stripping for write-backs and multiple block sizes [WANG89, WANB90]. Agarwal and Huffman introduce a technique that eliminates references by exploiting spatial locality [AGAH90].

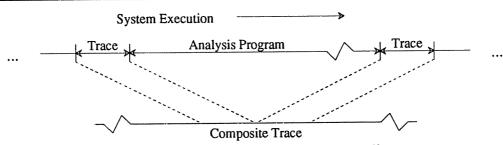

Sampling techniques also reduce trace data requirements. Their cost is also an information loss. Puzak introduced *set sampling* (congruence class sampling), which eliminates all full trace references except those to the sampled sets. The sampled sets estimate the performance of all cache sets. Laha, et al. [LAPI88] advocate *time sampling*, using many short time-samples of a full trace to estimate cache performance. Individual time-samples can be statistically combined to produce a picture of the full trace. Chapter 4 analyzes both set sampling and time sampling in detail.

## 2.4.3.2. Cache Analysis Using Address Traces

Many previous studies of uniprocessor cache performance used address traces, far too many to reference them all in this document. For one example, the first paper describing the details of a CPU cache, the one describing the IBM 360 Model 85 cache [LIPT68], included trace-driven simulation results to validate their design choices. In another example study, Kaplan and Winder show the performance tradeoffs of different cache configurations [KAPW73]. A milestone in CPU cache research was reached with the survey of Smith [SMIT82]. This survey examines many basic aspects of cache design, including replacement policy, write policy, block size, and virtual versus real indexing. The block size analysis was later expanded [SMIT87]. Smith also presents an extensive bibliography [SMIT86] of studies on the topic of CPU caches, many of these papers are described in his survey.

Easton and Fagin point out a danger of trace-driven simulation: the cold-start problem [EASF78]. When traces are short, cache initialization effects may dominate performance, particularly with large caches. Since the multi-megabyte caches considered in this dissertation exacerbate the cold-start problem over that of smaller caches, Chapters 3 and 4 pay particular attention to cold start. Except in Section 4.3, all miss frequency results given in this dissertation are cold start, that is, they assume the cache starts from the empty state at the beginning of a simulation. Cold-start biases the results by at most a few percent because the traces that are used are very long.

Recent studies by Hill [HILL87, HILL88] and Przybylski, et al. [PRZY88, PRHH88] characterize the performance of various cache configurations. They point out that higher associativity does not necessarily mean better performance since more associativity may increase the time it takes to retrieve data from the cache. Hill and Smith [HILS89] further analyze associativity by classifying misses as one of three types: conflict, capacity, or compulsory. Conflict misses could be eliminated with higher associativity and serve as a measure of the potential usefulness of associativity. Capacity misses are due to limited cache size, and compulsory misses are due to the first references to cache blocks. Przybylski has also examined the impact of different block sizes and fetch policies [PRZY90].

Przybylski, et al. further point out that there is a limit on the average speed (hits and misses) that can be achieved with a single level cache [PRHH88]. While larger caches have fewer misses, they are slower. Beyond some point, multi-level caching is required to improve average access time.

Short and Levy present simulation results of multi-level cache configurations [SHOL88]. The results show that multiple levels caches give good performance and that write-back caches may give the highest performance. Baer and Wang [BAEW88] present the necessary requirements to implement a very restrictive form of *inclusion* in a cache hierarchy. The study of multi-level cache configurations by

Przybylski, et al., [PRHH89] points out that the frequency of cache misses in a secondary cache is largely independent of the lower level caches provided the cache is sufficiently large compared to the size of the upstream caches (about eight times). They also mention that secondary caches need not be as fast as primary caches (since they are not accessed on all memory references). Higher associativity and larger cache size is more useful in secondary caches since slower data withdrawal can be tolerated to reduce the frequency of misses. Slow implementations of associativity may even be useful in secondary caches, as pointed out by Kessler, et al., [KEJL89]. Wang, et al., [WABL89] present organizational details and simulation results of a multi-level virtual-real cache hierarchy that maintains inclusion. Borg, et al., present simulation results of multi-level cache configurations with multi-megabyte caches, and show that long traces are useful for the analysis of large caches [BOKL89, BOKW90]. Mogul and Borg further consider the costs of context switching in large caches [MOGB91]. Bugge, et al., also analyze design considerations of large caches [BUKB90]. Mudge, et al., also discuss some cache design considerations of a high-performance uniprocessor [MUBB91, OLMB91]. Chapter 5 discusses many of these design considerations for multi-megabyte caches.

### 2.5. Cache Performance Metrics

With a multi-level cache hierarchy, an analysis of the performance of the configuration can be difficult because there are many components. Each component of the memory system has an impact on overall performance; thus, a performance metric that can isolate the effects of each is needed. Optimization of the performance metric also should correspond to minimization of the total execution time of the workload.

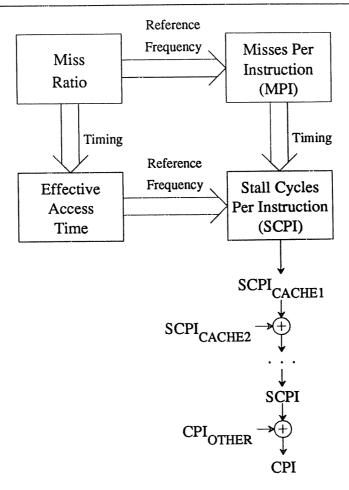

Figure 2.4 depicts the relationship between four different cache performance metrics. Miss ratio, the cache misses divided by the number of times the cache is referenced, is the most commonly used one. Miss ratio is a simple and intuitive measure of the way a cache is performing. Unfortunately, miss ratio is often inadequate for optimizing cache designs; minimal miss ratio does not imply maximal performance because miss ratio does not factor in cache timing parameters (hit and miss times) and usage frequency (how often the cache is referenced).

Effective access time is a measure of the average amount of time required to access a memory location using a cache. It adds timing information to the miss ratio estimate. Effective access time is a superior metric to compare different cache configurations when the timing changes from one configuration to the next one: a lower effective access time implies better performance.

Though effective access time cures one problem with miss ratio, it also may be inadequate, particularly for cache configurations with multiple caches like the multi-level cache hierarchy examined in this dissertation. The problem with effective access time is that it does not consider cache access frequency. Consequently, it may not gauge the effect of a cache on overall system performance. For example, a secondary cache may have a considerably higher effective access time than a primary cache. This does not mean that the secondary caches are performing more poorly than the primary caches. On the contrary, secondary cache misses may still have a smaller effect on the execution speed of the processor because the primary caches are referenced much more frequently.

This dissertation uses the performance metrics shown on the right side of Figure 2.4, misses per instruction MPI and stall cycles per instruction SCPI, because they correctly factor in the frequency of the cache accesses. This is essential when considering the multiple caches of a multi-level hierarchy. SCPI measures the average impact of cache misses on the execution of each instruction. SCPI is one

Figure 2.4. Cache Performance Metrics.

This figure shows the relationship between four alternative cache performance metrics.

component needed to estimate *CPI*, or the average cycles required to execute each instruction. (Hennessy and Patterson use *SCPI* to calculate *CPI* in this way [HENP90].) It puts each of the instruction, data, and secondary caches in their proper perspective in the hierarchy as a whole; it allows the performance effects each cache to be compared with the other caches, and with alternative implementations of the same cache.

Chapters 3 and 4 focus on techniques to estimate MPI. MPI is important because it, along with timing information, is needed to calculate SCPI. Chapter 5 adds in timing to the MPI estimates, producing SCPI, so that alternative cache designs can be compared. This dissertation then reverses itself (from a metrics standpoint), and Chapter 6 focuses again on MPI. Chapter 6 considers only software techniques to improve cache performance; the timing analysis is not required because software cannot change the hardware timing.

This dissertation uses a simple *SCPI* calculation. Each CPU cache in the hierarchy adds a component to the total SCPI:

$$SCPI_i = MPI_i \times Tmiss_i.$$

(2.1)

$MPI_i$  is the misses per instruction from cache i and  $Tmiss_i$  is the average time taken to service miss (in

cycles) in cache i, the miss penalty<sup>3</sup>. The total SCPI for a hierarchical cache configuration is:

$$SCPI = \sum_{i \in HIERARCHY} SCPI_i \tag{2.2}$$

with i ranging over the caches in the hierarchy. For the two level configuration in this dissertation (Figure 1.1 on the right):

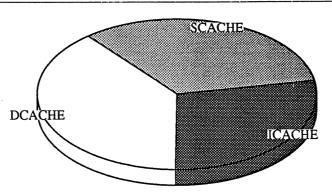

$$SCPI = SCPI_{ICACHE} + SCPI_{DCACHE} + SCPI_{SCACHE}$$

.

It measures the average cycles lost because of cache misses, an important component of the execution time of a traced workload. *SCPI* is closely related to the *CMC* of [BUKB90]. Ideally, *SCPI* should be small relative to the average cycles taken to execute each instruction, so the processor speed determines the execution speed. With a high *SCPI*, system speed would be dominated by the memory system performance, rather than the processor performance.

Note that the calculation of  $SCPI_i$  in Equation 2.1 assumes a constant miss penalty. This is an approximation of the true effects of each miss. In particular, the costs of write-backs are not modeled. A write-buffer that performs the writes "in the background" is assumed; it allows the processor to continue while the write is being completed. Without a write buffer, the performance loss from dirty misses would be higher since the dirty block needs to be removed before the new one is fetched. With a write-buffer, the processor need only stall when the write-buffer is not successful in hiding the latency of the write. In the SCPI calculation, a perfect write-buffer is assumed. This assumption is realistic for large write-buffers [PRHH89].

The weakness with this calculation of *SCPI* is that it does not count some important memory system performance effects. For example, I/O latencies to support virtual memory are neglected to restrict the scope to CPU cache performance. *SCPI* may include miss latencies that could be eliminated by overlapping with other operations. This dissertation does not consider lockup-free caches, which allow miss latencies to be overlapped with other cache hits [KROF81, SOHF91]. It also does not consider that on a cache miss the requested data could be returned first, satisfying a reference early and allowing the processor to continue rather than waiting for an entire cache block to be fetched, which also allows miss latencies to be overlapped. This overlapping could make *Tmiss* a pessimistic estimate of the actual time for a miss; consequently, *SCPI* would be pessimistic. On the other hand, *SCPI* also may be an optimistic estimate of CPU cache performance since contention (because of dynamic memory refresh, or I/O requirements) for memory resources is not factored into Equation 2.1. That is, queueing delay for main memory is not considered. Contention could increase the time for a cache miss, making both *Tmiss* and *SCPI* optimistic.

Despite its shortfalls, SCPI is a powerful CPU cache performance analysis tool for multi-level cache hierarchies. First, it is simple, and can be calculated with only the MPI and Tmiss of each cache in the configuration. SCPI abstracts many implementation details of a real system. The results are not dependent on the issue rate of the processor, for example, so they are equally valid for a superscalar processor as one that can only issue a single instruction per cycle. Despite its abstraction, SCPI is a reasonable estimator of the overall performance of a given CPU cache configuration. Another advantage is that breaking SCPI into its constituents isolates the importance of each component to the system performance as a whole. The relative magnitude of each component of SCPI emphasizes the importance of

<sup>3.</sup> The miss penalty of the primary caches is the time for a secondary cache hit.

the corresponding cache misses to overall system performance and can be used to direct efforts toward performance improvement. By abstracting details, *SCPI* allows attention to be narrowed to the most fundamental factors in cache performance.

In this study,  $Tmiss_{ICACHE} = Tmiss_{DCACHE} = 10$  cycles.  $Tmiss_{SCACHE}$  will range from 30 to 200 cycles for different cache configurations, with a default of 100. The default parameters, for example, could correspond to a processor with a 5-nanosecond (ns) cycle time, where 50-ns is required to transfer a 32-byte block from the secondary to the primary caches, and 500-ns is required to transfer a main memory block of 128-bytes to the secondary cache, as depicted in Figure 1.1.

## 2.6. Statistical Techniques

Statistical techniques are used for two purposes in this dissertation: (1) to measure sampling errors (in Chapter 4); and (2) to establish the level of confidence in results (Chapter 4 and Appendix B).

Chapter 4 uses several sampling error measurement techniques, depending on the situation. When there is only a single estimate that is to be compared to a true value, a good error measure is the relative error:  $\frac{(MPI_{estimate} - MPI_{true})}{MPI_{true}}$ , where  $MPI_{true}$  is the true value and  $MPI_{estimate}$  is the estimate. When there are multiple estimates, a better measure is the coefficient of variation of the estimates:

$$CV = \frac{\sqrt{\frac{1}{n} \sum_{j=1}^{n} (MPI_j - MPI_{true})^2}}{MPI_{true}},$$

(2.3)

where  $MPI_j$  is the j-th of n estimates. This coefficient of variation is used to measure the average sampling errors in this dissertation when all n=N out of N possible samples are available, or when  $\frac{1}{n} \sum_{j=1}^{n} MPI_j = MPI_{true}.$  The coefficient of variation is the standard deviation (or the root-mean-squared error) divided by the mean.

When sampling is used in practice,  $MPI_{true}$  is estimated with  $MPI_{mean} = \sum_{j=1}^{n} MPI_{j}$ , where n is the number of estimates gathered ( $n \le N$ ). To establish confidence that  $MPI_{mean}$  is near  $MPI_{true}$  without knowing the value of  $MPI_{true}$ , it is useful to calculate a 90% confidence interval. Chapter 4 and Appendix B use simple statistical techniques to calculate 90% confidence intervals for  $MPI_{true}$ , assuming that the  $MPI_{j}$  estimates are normally distributed and independent<sup>4</sup>. To calculate the confidence intervals, the coefficient of variation of the mean of a sample of size n from a (possibly) finite population of size N is first estimated:

$$CVEST_{mean} = \frac{\sqrt{\frac{1}{n-1} \sum_{j=1}^{n} (MPI_j - MPI_{mean})^2}}{MPI_{mean} \sqrt{n}} \sqrt{\frac{N-n}{N-1}}.$$

(2.4)

This equation calculates  $CVEST_{mean}$  (the estimated coefficient of variation of  $MPI_{mean}$ ) similar to the way Equation 2.3 calculates CV, but it reduces it by a  $\frac{1}{\sqrt{n}}$  factor because  $MPI_{mean}$  is the mean of n

<sup>4.</sup> The central-limit theorem suggests that the normal assumption is accurate when the sample size (n) is large, or when  $MPI_{ij}$  is the sum of many random variables [MILF77].

$MPI_j$ 's.  $\sqrt{\frac{N-n}{N-1}}$  is a finite population correction factor [MILF77], which is only needed when n is close to N, because in other cases it is close to one. Note that this correction implies that  $CVEST_{mean}$  approaches zero as n approaches N because  $MPI_{mean} = MPI_{true}$  when n = N. (This correction is not needed in Appendix B because N is very large.) If  $CVEST_{mean}$  were exact, the normal distribution would be directly used to estimate confidence intervals, but since  $CVEST_{mean}$  is an estimate, the student-t distribution is used. Using the student-t,  $MPI_{true}$  is bounded (with 90% confidence) below by  $MPI_{mean}(1 - t_{90\%,n-1}CVEST_{mean})$  and above by  $MPI_{mean}(1 + t_{90\%,n-1}CVEST_{mean})$ .  $t_{90\%,n-1}$  is the value of the student-t statistic that has a tail of 5% (on each end) for n-1 degrees of freedom. For example,  $t_{90\%,n-1} = 1.833$  for n = 10. Note that the confidence interval is centered around  $MPI_{mean}$ . If the  $MPI_j$  estimates are nearly normally distributed, or if n is large,  $MPI_{true}$  will be within this interval 90% of the time.

### 2.7. The Trace-Driven Simulation Environment

Trace-driven simulation provides accurate results for a variety of cache configurations, but its cost is large simulation times, particularly for the trace lengths needed with multi-megabyte caches. One alternative for more efficient simulation would be to use an algorithm that produces many results with a single pass through the trace data. This algorithm, called *stack simulation*, was pioneered by Mattson, et al., [MAGS70]. Thompson and Smith extended stack-simulation so that write-back traffic could be calculated, in addition to the miss ratio [THOS89]. Concurrently, Hill and Smith also extended stack simulation in several ways [HILL87, HILS89]: *forest simulation* gathers results for several direct-mapped caches concurrently, and *all-associativity simulation* simulates multiple set-associative caches concurrently. Wang and Baer combined these extensions, introducing an all-associativity simulation algorithm that produces write-traffic results in addition to miss ratios [WANG89, WANB90].

These simulation techniques can reduce simulation times, but they have a cost. One disadvantage is their increased complexity. Also, though stack simulation has been extended for write-back traffic in addition to miss ratios, it still restricts the performance metrics that can be gathered during a simulation. Another disadvantage is their large memory requirements. Memory requirements are particularly important when simulating multi-megabyte caches; they can even dominate other concerns.

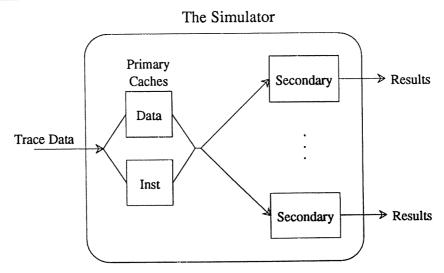

An alternative technique for fast simulation takes advantage of the homogeneity inherent in multiple simulations of hierarchical cache configurations. Since the primary cache configuration is constant throughout this dissertation, and its behavior is often independent of the secondary cache configuration, multiple secondary caches can usually be simulated while simulating the primary cache only once. Figure 2.5 depicts this idea. Since the primary caches satisfy most of the references, most of the simulation time is spent on the primary caches. Eliminating these simulations is a big savings. Many secondary simulations can be completed with a single primary simulation. A concern with this implementation is that the simulator requires a large amount of memory. This concern was alleviated by minimizing the storage required to simulate each cache block frame. Usually, only a single word (4-bytes) is required per block, so even a 16-megabyte secondary cache simulation (with 128-byte blocks) needs only 512-kilobytes.

The homogeneity in Figure 2.5 saves much simulation time at no accuracy loss. The same effect could be extracted by saving primary cache misses (and write-backs!) when simulating only the primary caches, and later simulating the secondary caches using the saved references. This extraction is

Figure 2.5. Simulation of Homogeneous Hierarchical Configurations.

This figure shows the structure of the simulator. A single pair of primary caches is simulated, rather than one for each secondary configuration. The secondary cache references (from primary cache misses) are submitted independently to each secondary cache, and results are obtained for each.

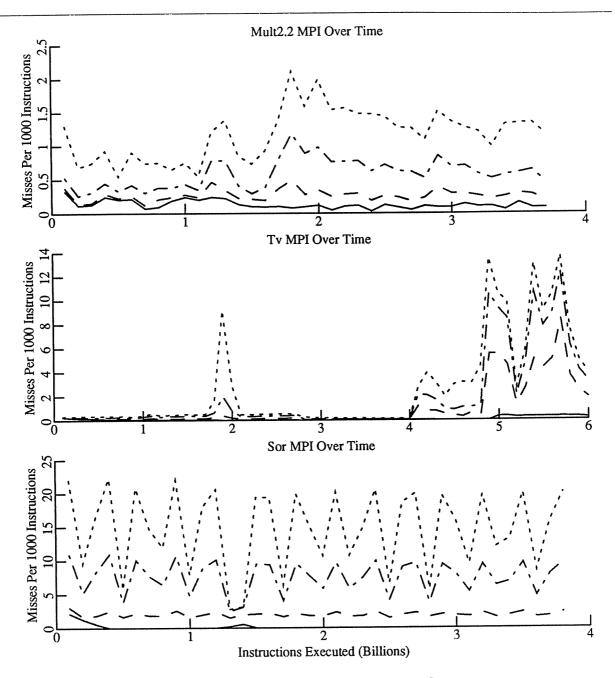

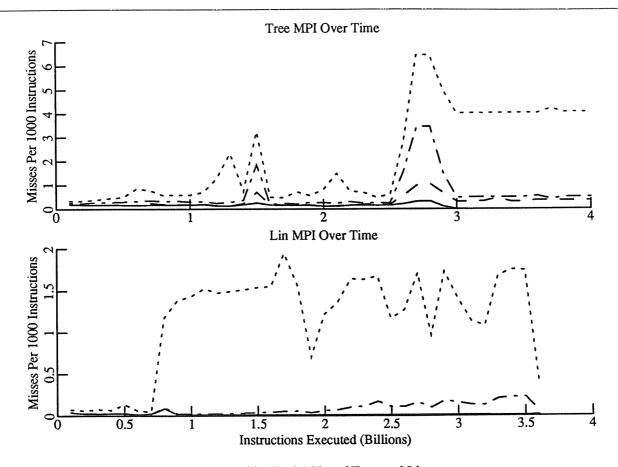

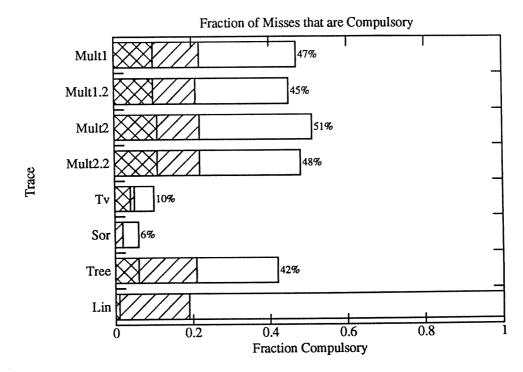

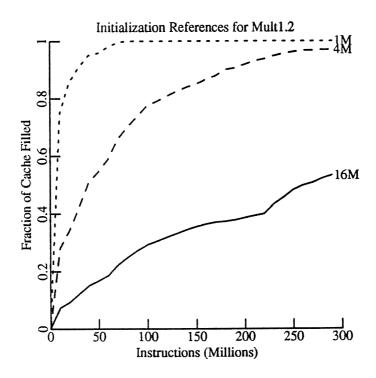

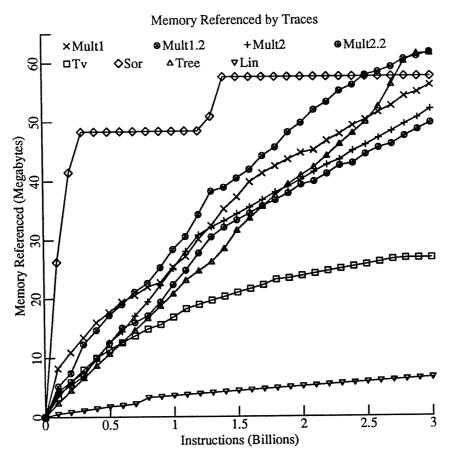

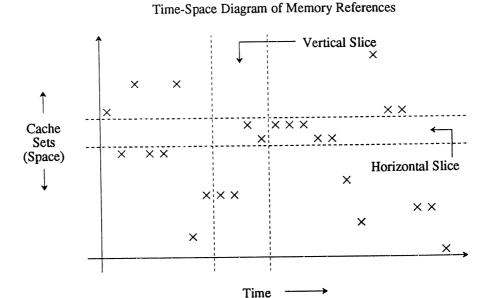

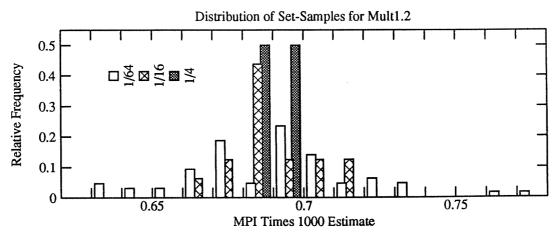

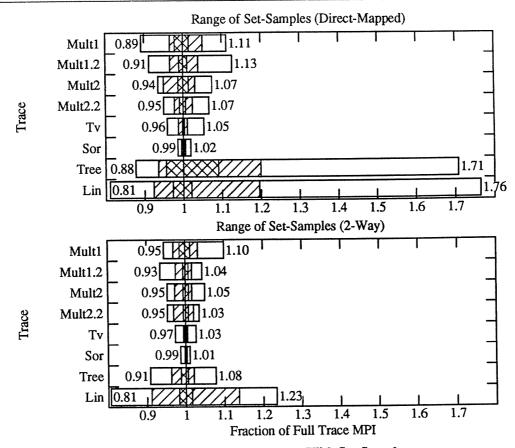

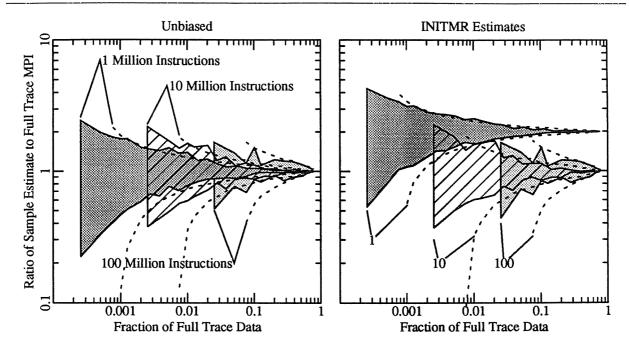

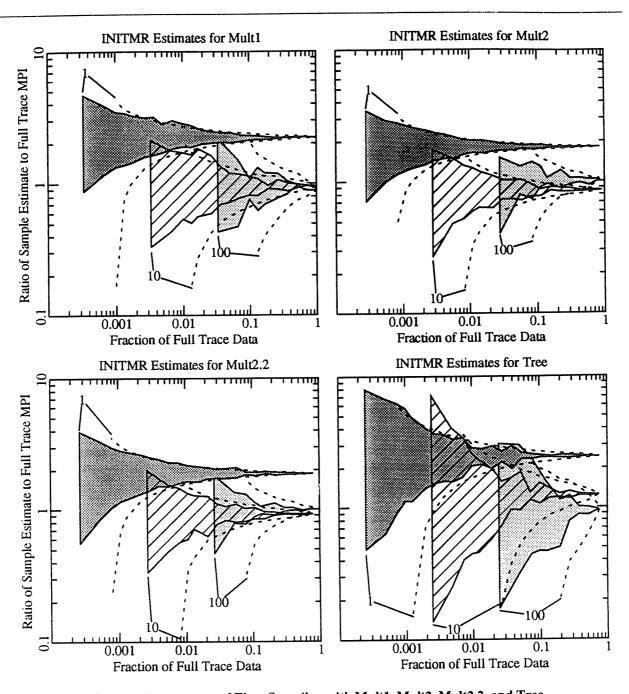

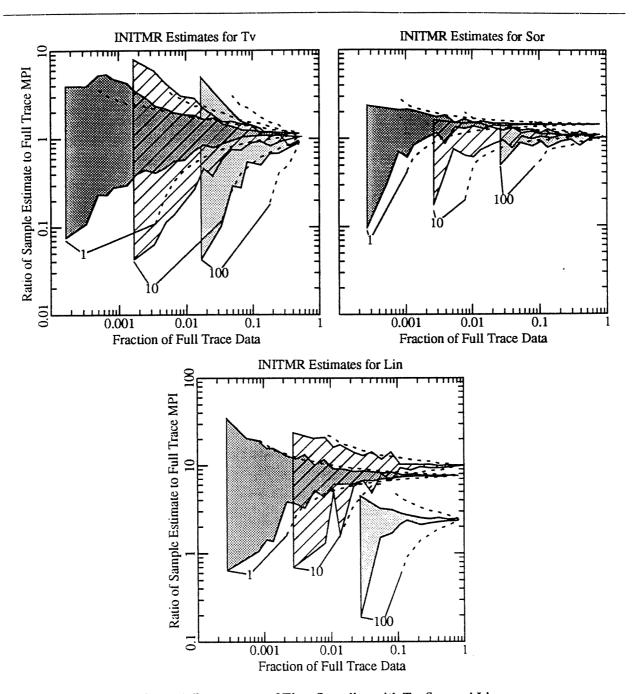

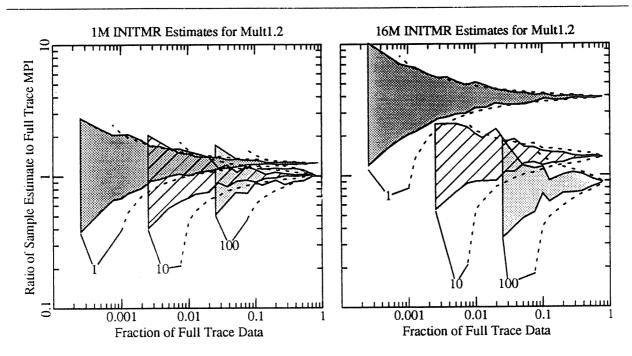

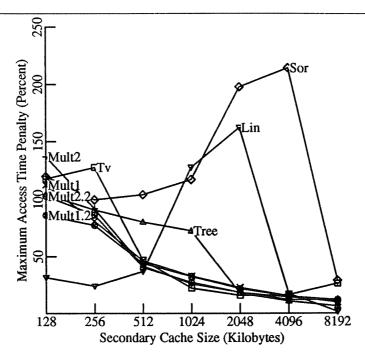

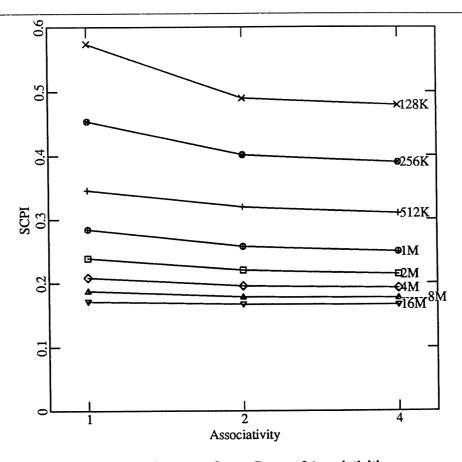

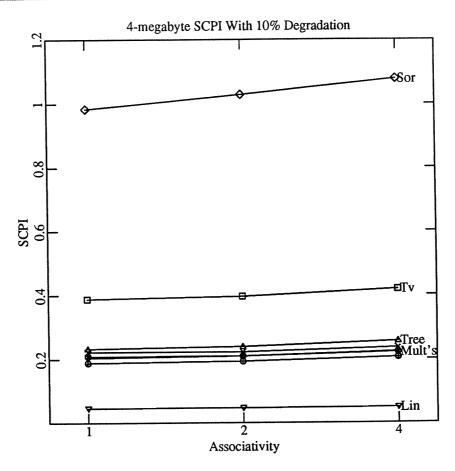

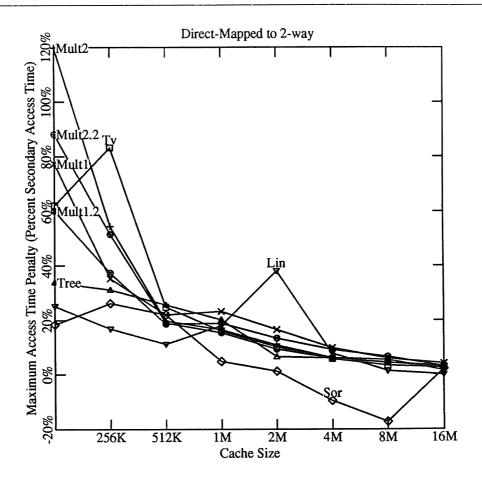

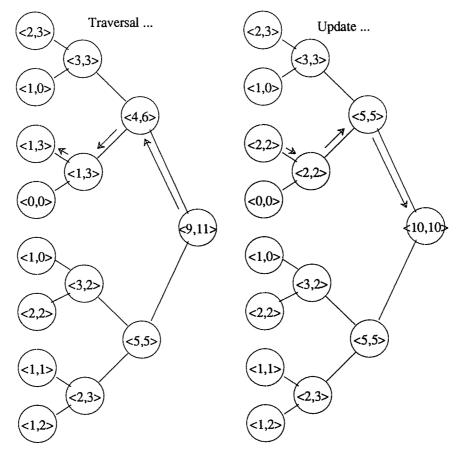

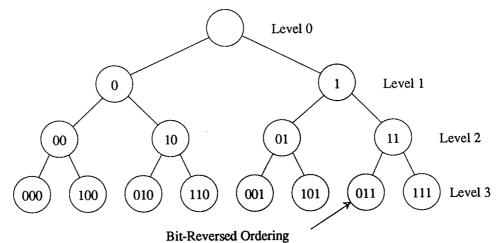

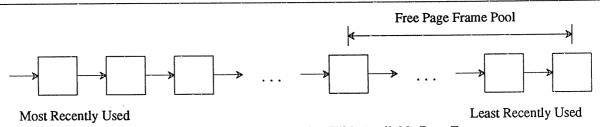

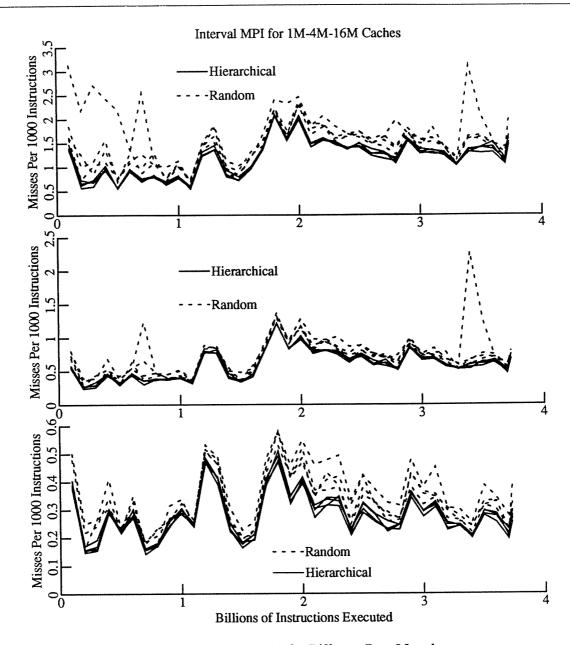

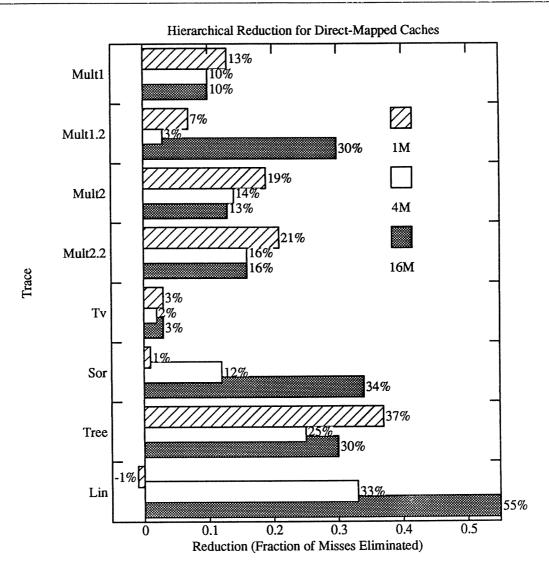

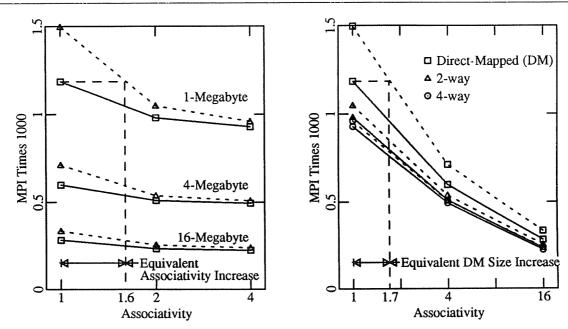

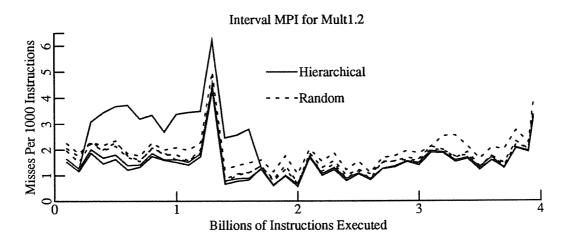

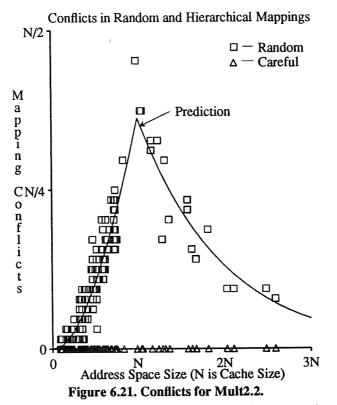

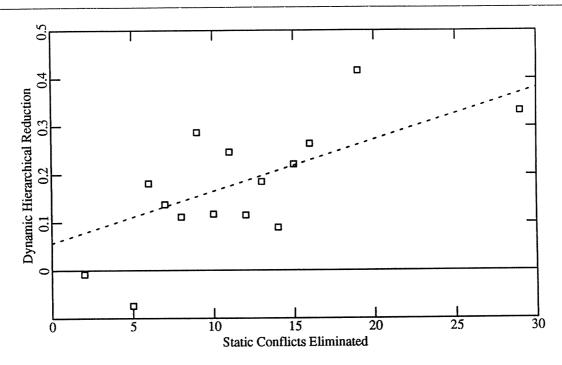

cumbersome when there are many intermediate traces, as is true for the simulations in Chapter 6, where each trace is modified by many different virtual to real address translations, producing many different traces. Another problem with saving the intermediate traces is that primary cache simulations are not always the same for all hierarchical configurations. For example, when enforcing inclusion between the primary and secondary cache levels (see Chapter 5), the primary cache behavior will be different for each secondary cache, and a brute-force simulation of each two-level configuration is required for precise results. The simulator in Figure 2.5 can adapt to the inclusion case by simulating only a single secondary cache configuration with each primary cache simulation, while an intermediate trace is completely inadequate for this case. Alternative techniques need to be used to speed up simulations when there is no primary cache homogeneity for different secondary caches.