## **Incorporating Guarded Execution into Existing Instruction Sets**

by

#### Dionisios N. Pnevmatikatos

A dissertation submitted in partial fulfillment of the requirements for the Degree of

**Doctor of Philosophy**

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

1996

#### **Incorporating Guarded Execution into Existing Instruction Sets**

Dionisios N. Pnevmatikatos UNIVERSITY OF WISCONSIN – MADISON, 1996 Under the supervision of Gurindar Sohi

Guarded execution, or simply guarding, is a powerful and promising concept, with the potential to reduce the unpredictability of the control flow caused by branches, and smoothen the flow of instructions in processor pipeline(s). Guarding also boosts the compiler's ability to expose instruction level parallelism to the processor, while requiring a modest amount of hardware support. These features make guarding attractive for inclusion in an architecture. However, the integration of guarding in an instruction set is not easy, especially when the designer needs to extend an existing instruction set. This thesis address two issues that are critical to the widespread acceptance for guarding: (i) the required instruction set support for guarded instructions, and (ii) the performance on aggressive processor configurations.

This thesis proposes GUARD instructions, a new class of instructions that offer an easy and powerful way to accommodate guarded execution in an instruction set. With the modest requirement of just a few opcodes, GUARD instructions are sufficient to provide efficient support for full guarding.

This thesis evaluates and compares the performance of three ways of supporting guarding: (i) using explicit guard operand fields in each instruction, (ii) using conditional move instructions, and (iii) the newly proposed GUARD instructions. The results of this evaluation show that for all configurations, GUARD instructions perform better than ordinary guarding. They also show that conditional moves can exploit a large fraction of the potential of full guarding, and that hardware mechanisms such as 2-level adaptive branch prediction and out-of-order execution diminish the performance potential of guarded execution.

Dedicated to my sister Maria Christina, who left us too soon

Αφιερωμένο στην αδερφή μου Μαρία Χριστίνα, που μας άφησε πολύ νωρίς

## **Acknowledgments**

Six and a half years and one winter too many in Madison. Thousands of hours of simulations, thousands of lines of code, and even more numbers to gather and interpret. All this work would not have been possible if it weren't for four people: my advisor Guri Sohi who taught me everything I know about research and paper writing, my wife Natalia who loved me, supported me and inspired me more than I could ever ask for, and my parents Nikos and Katerina who made everything in their power to provide me with the best education, even if it meant that we had to be separated. The unconditional support and encouragement of these four people kept me cruising along the long haul of the doctoral dissertation, and for that I will always be grateful. This thesis is as much a tribute to their efforts, as it is to mine.

I would like to thank the members of my thesis committee, Jim Goodman, Jim Smith, David Wood and Parmeswaran Ramanathan for their patience in reading my thesis and for their comments that made this thesis more accurate, more complete and easier to read. I would also like to thank Manolis Katevenis who taught me how much fun computer architecture can be, and Mark Hill who taught me pretty much everything there is to know about caches and introduced me to applied research (see 10+ day long simulations!).

I would also like to thank the members of the multiscalar group: Todd Austin, Scott Breach, Manoj Franklin, Andreas Moshovos, and T. N. Vijaykumar, and other students in architecture: Stefanos Kaxiras, Babak Falsafi with whom I had discussions about everything and anything, even about computer architecture! Todd Austin deserves a special mention both for our close cooperation on the Fast Address Calculation paper, and for his SimpleScalar simulation tools that I used in this thesis.

My life in Madison has been enriched by a number of new close friends: Dimitris Cholevas, Andreas Moshovos, Kyros Koutoulakos, Stefanos Kaxiras, Minos Garofalakis, Lakis Karmirantzos, Spyros Kontogiorgis, Yannis Christou and Yannis Schoinas. Guys, I should have ranked you according to coffee-break performance! Other people that I would like to acknowledge are Yannis Ioannidis, Giorgos Drettakis, Dimitra Vista, and all the members of the Hellenic Student Association of UW–Madison.

I would also like to thank the Wisconsin State Government agencies who's phones are 266-18xx, for making the simple task of answering the phone much more interesting and exciting. I think I will always remember the first "Office of Probation and Parole", "Sargent in Arms" and "Judge Wilcox Chambers" phone calls.

DIONISIOS N. PNEVMATIKATOS

# **Contents**

| Abstrac   | et                                                              | İ   |

|-----------|-----------------------------------------------------------------|-----|

| Acknov    | vledgments                                                      | iii |

| List of   | Tables                                                          | vi  |

| List of 1 | Figures                                                         | ix  |

| Chapte    | r 1 Introduction                                                | 1   |

| 1.1       | What can we do about branches?                                  | 1   |

| 1.2       | Guarding Background                                             | 2   |

| 1.3       | Contributions of this thesis                                    | 3   |

| Chapte    | r 2 Guarded Execution                                           | 5   |

| 2.1       | Semantics and use of guarded instructions                       | 5   |

|           | 2.1.1 Use of guarded instructions                               | 5   |

|           | 2.1.2 Advantages of guarding                                    | 7   |

|           | 2.1.3 Limitations of guarding                                   | 8   |

| 2.2       | Instruction set support for guarding                            | 9   |

|           | 2.2.1 Support for guard condition evaluation                    | 9   |

|           | 2.2.2 Support for specifying guarded computation                | 12  |

| 2.3       | Hardware support for guarding                                   | 16  |

|           | 2.3.1 Implementing guarding using select logic                  | 16  |

|           | 2.3.2 Implementing guarding by overloading the forwarding logic | 17  |

|           | 2.3.3 Implications of out-of-order execution                    | 17  |

| 2.4       | Summary                                                         | 21  |

| Chapte    | r 3 Compiling for guarded execution                             | 22  |

| 3.1       | Choosing what to guard                                          | 22  |

|           | 3.1.1 The Multiblock region selection scheme                    | 24  |

|           | 3.1.2 The Hyperblock region selection scheme                    | 25  |

| 3.2       | If-conversion basics                                            | 25  |

| 3.3       | Guarding-specific optimizations                                 | 27  |

|           | 3.3.1 Loop restructuring                                        | 29  |

|           | 3.3.2 Tail duplication                                          | 30  |

|           | 3.3.3 Loop peeling                                              | 31  |

|           | 3.3.4 Control-tree height reduction                             | 32  |

|           | 3.3.5 Condition evaluation optimizations                        |     |

|           | 2.2.6 Evit coologging                                           | 2/  |

|                          | 3.3.7 Predicate promotion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                               |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 3.4                      | Scheduling guarded code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                               |

| 3.5                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                               |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| -                        | 4 GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38                                                                               |

| 4.1                      | Semantics of GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                          | 4.1.1 A small example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|                          | 4.1.2 Features of GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                               |

| 4.2                      | ISA support for GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                               |

|                          | 4.2.1 New instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                               |

|                          | 4.2.2 New ISA state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                               |

|                          | 4.2.3 GUARD instruction use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43                                                                               |

| 4.3                      | GUARD instruction assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44                                                                               |

|                          | 4.3.1 An algorithm for determining GUARD masks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                               |

|                          | 4.3.2 An example of GUARD assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                                               |

| 4.4                      | Hardware considerations for GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                               |

|                          | 4.4.1 Interaction between GUARD and Branch instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52                                                                               |

|                          | 4.4.2 Interrupt handling and GUARD instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                                               |

| 4.5                      | Implications of out-of-order execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                               |

|                          | 4.5.1 Determining when a scalar mask bit is ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                               |

|                          | 4.5.2 Interaction of GUARD instructions and Branch prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                               |

| 4.6                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                               |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Chapter                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                               |

| Chapter 5.1              | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63                                                                               |

| -                        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>63                                                                         |

| -                        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>63                                                                         |

| -                        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>63<br>64<br>64                                                             |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>64                                                             |

| -                        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>63<br>64<br>64<br>65                                                       |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>64<br>65<br>66                                                 |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>65<br>66<br>66                                                 |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>65<br>66<br>68                                                 |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>65<br>66<br>66                                                 |

| 5.1                      | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>65<br>66<br>68                                                 |

| 5.1<br>5.2<br>5.3        | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead                                                                                                                                                                                                                     | 63<br>64<br>64<br>65<br>66<br>68<br>68                                           |

| 5.1<br>5.2<br>5.3        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>64<br>65<br>66<br>68<br>68<br>68                               |

| 5.1<br>5.2<br>5.3        | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead                                                                                                                                                                                                                     | 63<br>63<br>64<br>64<br>65<br>66<br>68<br>68<br>68<br>68                         |

| 5.1<br>5.2<br>5.3        | Motivation and metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63<br>64<br>64<br>65<br>66<br>68<br>68<br>68<br>69<br>70                         |

| 5.1<br>5.2<br>5.3        | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead  5.4.2 Branch counts  5.4.3 Effects on dynamic branch behavior                                                                                                                                                      | 63<br>63<br>64<br>64<br>65<br>66<br>68<br>68<br>68<br>69<br>70                   |

| 5.1<br>5.2<br>5.3<br>5.4 | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead  5.4.2 Branch counts  5.4.3 Effects on dynamic branch behavior  5.4.4 Guarding region characteristics                                                                                                               | 63<br>64<br>64<br>64<br>65<br>66<br>68<br>68<br>68<br>68<br>70<br>72             |

| 5.1<br>5.2<br>5.3<br>5.4 | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead  5.4.2 Branch counts  5.4.3 Effects on dynamic branch behavior  5.4.4 Guarding region characteristics  Effects of Conditional Moves                                                                                 | 63<br>64<br>64<br>64<br>65<br>66<br>68<br>68<br>68<br>67<br>70<br>77             |

| 5.1<br>5.2<br>5.3<br>5.4 | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead  5.4.2 Branch counts  5.4.3 Effects on dynamic branch behavior  5.4.4 Guarding region characteristics  Effects of Conditional Moves  5.5.1 Conditional Move guarding overhead                                       | 63<br>64<br>64<br>64<br>65<br>66<br>68<br>68<br>69<br>70<br>72<br>77             |

| 5.1<br>5.2<br>5.3<br>5.4 | Motivation and metrics  5.1.1 Guarding overhead  5.1.2 Branch counts  5.1.3 Dynamic branch behavior  5.1.4 Guarding region characteristics Related work  Methodology  5.3.1 Compilation techniques  5.3.2 Simulation techniques  5.3.3 Benchmark programs  Effects of full guarding  5.4.1 Guarding overhead  5.4.2 Branch counts  5.4.3 Effects on dynamic branch behavior  5.4.4 Guarding region characteristics  Effects of Conditional Moves  5.5.1 Conditional Move guarding overhead  5.5.2 Conditional Move branch counts | 63<br>64<br>64<br>64<br>65<br>68<br>68<br>68<br>68<br>70<br>72<br>77<br>77<br>77 |

|          | 5.6.2 Overh    | ead of GUAR     | D instruction | ons        |         |     |    |  |  |  |  | <br>83  |

|----------|----------------|-----------------|---------------|------------|---------|-----|----|--|--|--|--|---------|

| 5.7      | Summary        |                 |               |            |         |     |    |  |  |  |  | <br>85  |

| Chapter  | 6 Effects of   | guarding on     | execution     | time       |         |     |    |  |  |  |  | 86      |

| 6.1      | Simulation Mo  | ethodology .    |               |            |         |     |    |  |  |  |  | <br>86  |

|          | 6.1.1 In-ord   | er execution    | model         |            |         |     |    |  |  |  |  | <br>86  |

|          | 6.1.2 Out-of   | f-order execu   | tion model    |            |         |     |    |  |  |  |  | <br>87  |

|          | 6.1.3 Functi   | onal unit late  | ncies         |            |         |     |    |  |  |  |  | <br>87  |

|          | 6.1.4 Metric   | s               |               |            |         |     |    |  |  |  |  | <br>88  |

| 6.2      | Performance of | of guarding fo  | or an in-orde | er issue p | rocesso | or. |    |  |  |  |  | <br>88  |

|          | 6.2.1 Perfor   | mance of full   | guarding .    |            |         |     |    |  |  |  |  | <br>88  |

|          | 6.2.2 Perfor   | mance of gua    | arding using  | g conditio | nal mo  | ves |    |  |  |  |  | <br>91  |

|          | 6.2.3 Perfor   | mance of Gu     | ARD instru    | ctions .   |         |     |    |  |  |  |  | <br>93  |

| 6.3      | Impact of mis  | prediction per  | nalty         |            |         |     |    |  |  |  |  | <br>98  |

| 6.4      | Evaluation of  | guarding on a   | an out-of-or  | der exect  | ution n | ode | ۱. |  |  |  |  | <br>100 |

|          | 6.4.1 Impac    | t of limited si | ize referenc  | e counter  | ·s      |     |    |  |  |  |  | <br>102 |

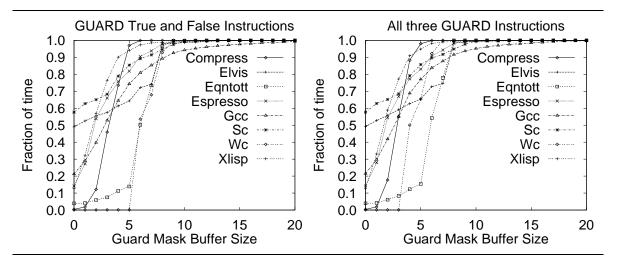

|          | 6.4.2 Impac    | t of a limited  | size Guard    | Mask Bu    | ıffer . |     |    |  |  |  |  | <br>103 |

| 6.5      | Summary        |                 |               |            |         |     |    |  |  |  |  | <br>105 |

| Chapter  | 7 Conclusio    | ns              |               |            |         |     |    |  |  |  |  | 107     |

| 7.1      | Comparison w   | ith the IMPA    | CT work .     |            |         |     |    |  |  |  |  | <br>108 |

| 7.2      | Future work    |                 |               |            |         |     |    |  |  |  |  |         |

| Bibliogr | aphy           |                 |               |            |         |     |    |  |  |  |  | 110     |

# **List of Tables**

| 2.1<br>2.2 | Advantages and limitations of guarding                                                   | 9<br>11 |

|------------|------------------------------------------------------------------------------------------|---------|

| 2.3        | Synthesis of general guarded statements using conditional move instructions              | 15      |

| 3.1        | The R mapping assigns a guard register to each basic block                               | 28      |

| 3.2        | The K mapping determines where each guard register should be set                         | 28      |

| 3.3        | Categorization of if-conversion specific optimizations.                                  | 29      |

| 4.1        | GUARD instruction assignment                                                             |         |

| 4.2        | Interactions between guarding regions and branches.                                      | 55      |

| 4.3        | Interrupt handling options with GUARD instructions                                       | 56      |

| 5.1        | Benchmark programs and their command lines and inputs.                                   | 69      |

| 5.2        | Instruction counts and overhead of guarding                                              | 69      |

| 5.3        | Instruction mix for the guarded benchmark programs                                       | 70      |

| 5.4        | Breakdown of branches according to branch type                                           | 71      |

| 5.5        | Dynamic branch counts and percent of branch reduction                                    | 71      |

| 5.6        | Effects of guarding on the misprediction statistics for a counter-based predictor        | 73      |

| 5.7        | Effects of guarding on the misprediction statistics for a correlation-based predictor    | 74      |

| 5.8        | Basic block, run-length and misprediction distance for full guarding                     | 76      |

| 5.9        | Static and dynamic guarding statistics                                                   | 77      |

| 5.10       | Instruction counts and overhead of conditional moves                                     | 78      |

|            | Dynamic branch counts and branch reduction for conditional moves                         | 79      |

| 5.12       | Effects of conditional moves on the misprediction statistics of a counter-based predic-  |         |

|            | tor                                                                                      | 80      |

| 5.13       | Effects of conditional moves on the misprediction statistics of a correlation-based pre- |         |

|            | dictor.                                                                                  | 80      |

| 5.14       | Basic block size, run-length and misprediction distance for conditional moves            | 81      |

|            | Dynamic Guard Statistics                                                                 | 83      |

| 5.16       | Overhead of GUARD instructions                                                           | 84      |

| 6.1        | Functional Unit Latencies                                                                | 88      |

| 6.2        | Execution time (in thousand cycles) and IPC for the original and the fully guarded pro-  |         |

|            | grams on a 4-issue processor using a counter-based predictor                             | 89      |

| 6.3        | Execution time (in thousand cycles) and IPC for the original and the fully guarded pro-  |         |

|            | grams on a 8-issue processor using a counter-based predictor                             | 90      |

| 6.4        | Execution time (in thousand cycles) and IPCs for the original and the fully guarded      |         |

|            | programs on a 4-issue processor using a correlation-based predictor                      | 91      |

| 6.5  | Execution time (in thousand cycles) and IPCs for the original and the fully guarded     |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | programs on a 8-issue processor using a correlation-based predictor                     | 92  |

| 6.6  | IPCs and speedup achieved by conditional move instructions for an 4-issue in-order      |     |

|      | processor using a counter-based predictor                                               | 92  |

| 6.7  | IPCs and speedup achieved by conditional move instructions for an 8-issue in-order      |     |

|      | processor using a counter-based predictor                                               | 93  |

| 6.8  | IPCs and speedup achieved by conditional move instructions for an 4-issue in-order      |     |

|      | processor using a correlation-based predictor.                                          | 94  |

| 6.9  | IPCs and speedup achieved by conditional move instructions for an 8-issue in-order      |     |

|      | processor using a correlation-based predictor.                                          | 94  |

| 6.10 | GUARD speedups compared to the speedups obtained using explicit guard conditions,       |     |

|      | for the counter-based predictor.                                                        | 96  |

| 6.11 | GUARD speedups compared to the speedups obtained using explicit guard conditions,       |     |

|      | for the correlation-based predictor.                                                    | 97  |

| 6 12 | Percent of instructions that can be squashed before they are fetched.                   | 98  |

|      | Effect of misprediction penalty on the guarding speedups for a 4-issue processor using  | ,   |

| 0.13 | a counter-based branch predictor.                                                       | 99  |

| 6 1/ | Effect of misprediction penalty on the guarding speedups for an 8-issue processor using | ,,  |

| 0.14 |                                                                                         | 100 |

| c 15 | •                                                                                       | 100 |

| 0.13 | Effect of misprediction penalty on the guarding speedups for a 4-issue processor using  | 101 |

| . 1. | a correlation-based branch predictor.                                                   | 101 |

| 6.16 | Effect of misprediction penalty on the guarding speedups for a 8-issue processor using  |     |

|      | a correlation-based branch predictor.                                                   | 101 |

| 6.17 | Execution time and IPCs for the original and guarded programs and on a 4-issue, out-    |     |

|      | of-order issue processor.                                                               |     |

| 6.18 | Impact of the Guard Mask Buffer size on the execution time                              | 105 |

# **List of Figures**

| 2.1  | A small loop and its corresponding CFG                                            | 6  |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | MIPS-like assembly for the code in Figure 2.1                                     |    |

| 2.3  | An example of multiple guard register sets and guard register initializations     | 10 |

| 2.4  | The MIPS R2000 instruction formats                                                | 16 |

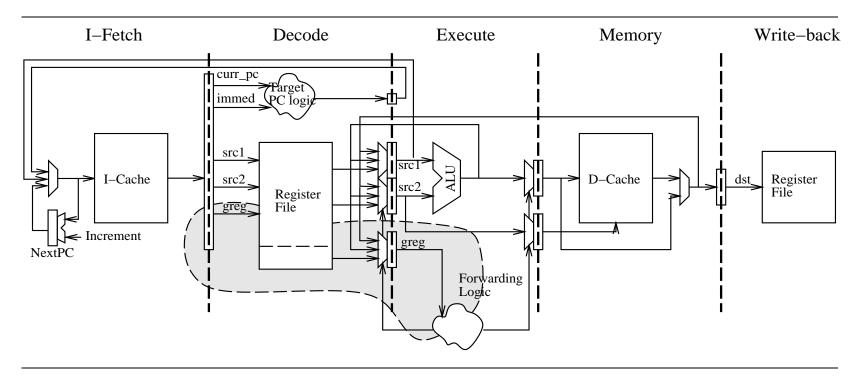

| 2.5  | A 5-stage pipeline implementing guarding using select logic                       | 18 |

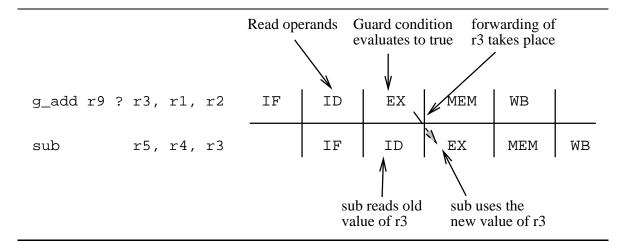

| 2.6  | Pipeline operation when the condition of a guarded instruction evaluates to true  | 19 |

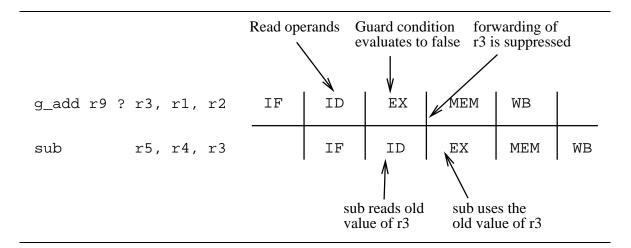

| 2.7  | Pipeline operation when the condition of a guarded instruction evaluates to false | 19 |

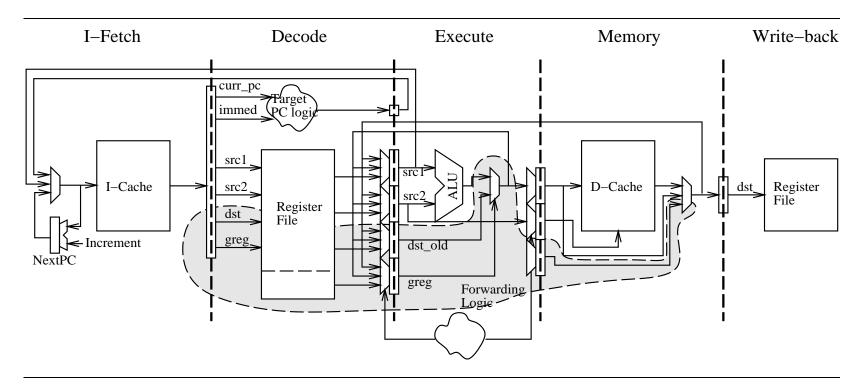

| 2.8  | A 5-stage pipeline implementing guarding overloading the forwarding logic         | 20 |

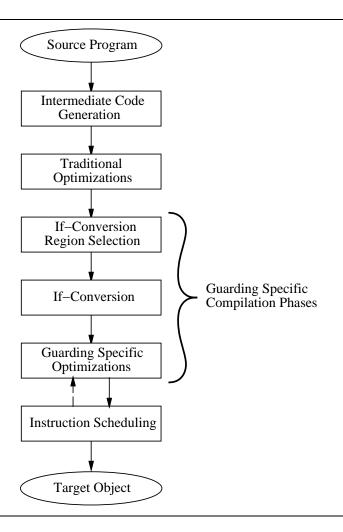

| 3.1  | The structure of an if-converting compiler                                        |    |

| 3.2  | 0                                                                                 |    |

| 3.3  | The if-conversion algorithm.                                                      | 27 |

| 3.4  | Condition register assignment and definitions by the RK algorithm                 | 28 |

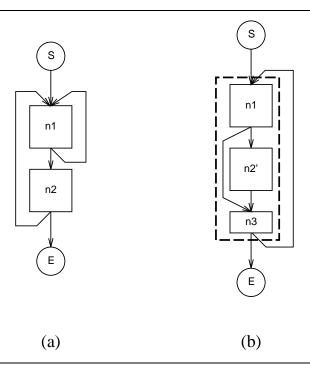

| 3.5  | Loop restructuring example                                                        | 30 |

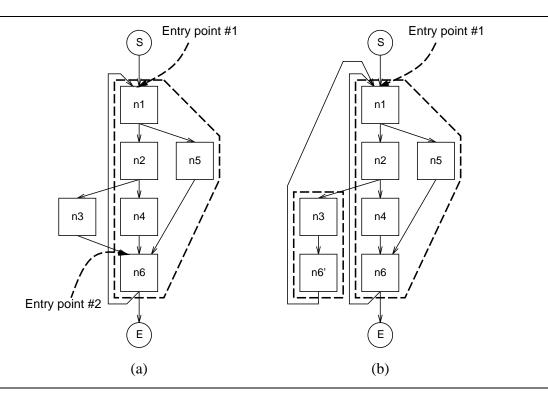

| 3.6  | Tail duplication example                                                          | 31 |

| 3.7  | Loop peeling example                                                              |    |

| 3.8  | Short circuit condition evaluation                                                | 33 |

| 3.9  | Condition evaluation using control-tree height reduction                          | 34 |

|      | Condition evaluation using pred_set instructions.                                 | 34 |

|      | Condition evaluation optimization for an if-then-else statement                   | 34 |

|      | Exit coalescing example                                                           | 35 |

| 3.13 | Instruction promotion example                                                     | 36 |

| 4.1  | The use of GUARD instructions                                                     |    |

| 4.2  | The use of GUARD masks                                                            | 44 |

| 4.3  | GUARD instruction execution                                                       | 45 |

| 4.4  | An algorithm for GUARD instruction and mask assignment                            | 46 |

| 4.5  | An algorithm for GUARD instruction and mask assignment supporting GUARDBOTH       |    |

|      | instructions.                                                                     | 47 |

| 4.6  | A control flow graph annotated with GUARD instructions                            | 48 |

| 4.7  | Condition register assignment and definitions by the RK algorithm                 | 50 |

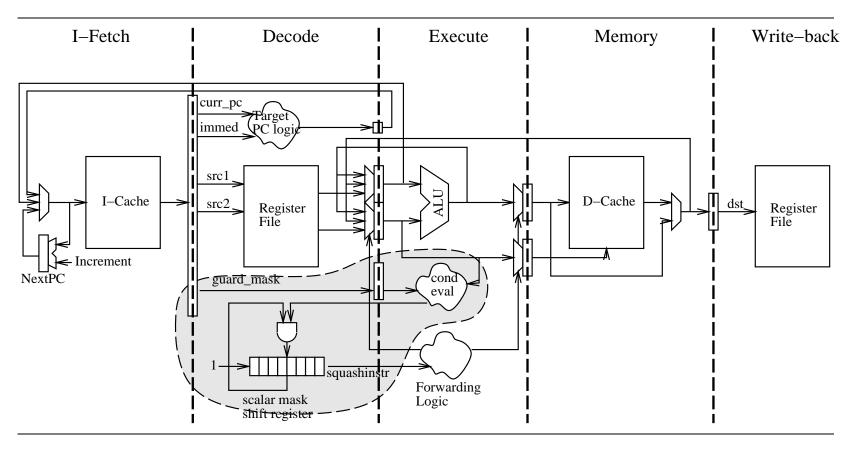

| 4.8  | A pipeline supporting GUARD instructions                                          | 51 |

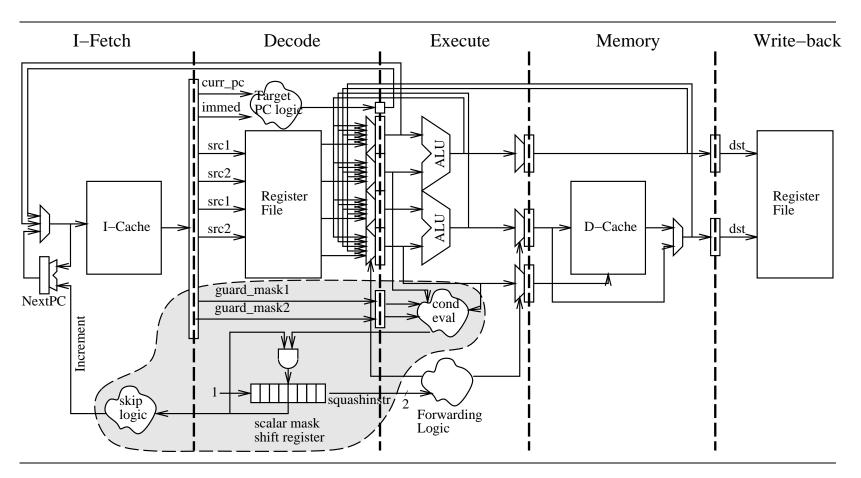

| 4.9  | A dual issue pipeline supporting GUARD instructions and a skip capability         |    |

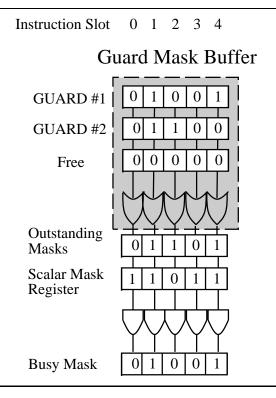

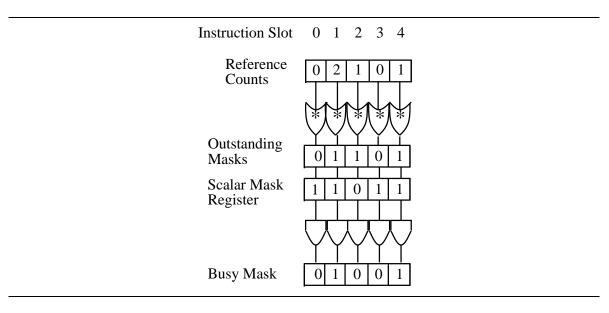

| 4.10 | Support for out-of-order execution of GUARD instructions: Guard Mask Buffer       | 57 |

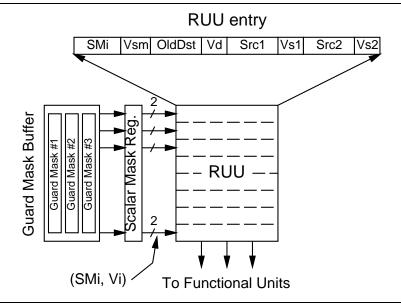

| 4.11 | Guard Mask Buffer and RUU                                                         | 58 |

|      |                                                                                   |    |

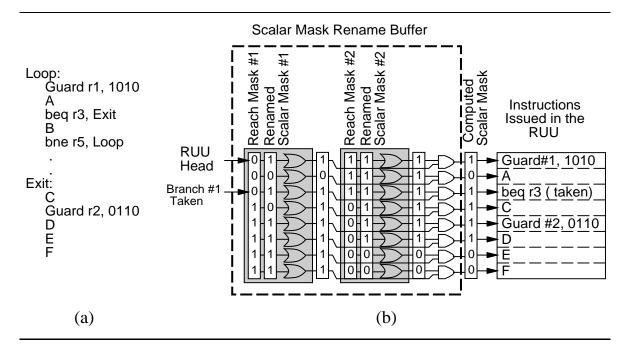

| 4.13 | Scalar Mask Rename Buffer                                                         | 60 |

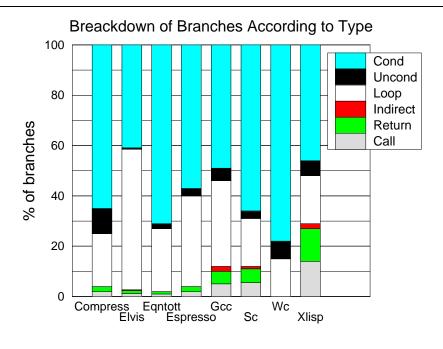

| 5.1  | Breakdown of branches according to branch type.                                   | 72 |

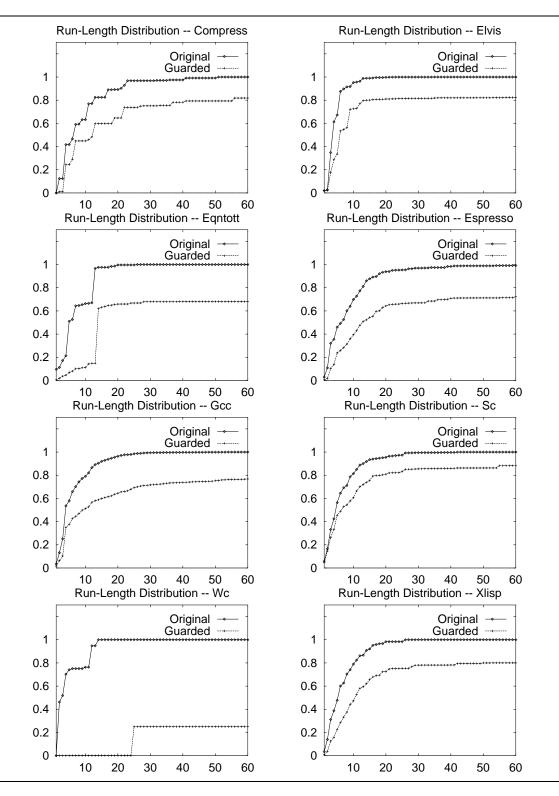

| 5.2 | Run-length distributions for the original and guarded benchmark programs | 75 |

|-----|--------------------------------------------------------------------------|----|

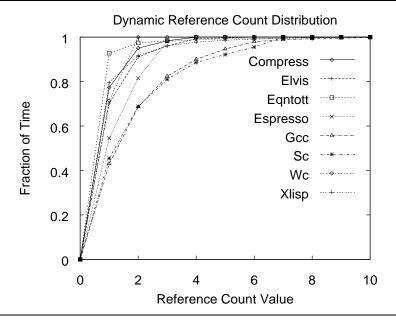

|     | Dynamic cumulative distribution of GUARD reference counts                |    |

# Chapter 1 Introduction

In the quest for ever-faster processors, and with a considerable transistor budget per chip, processor designers rely heavily on Instruction Level Parallelism (ILP) to achieve higher performance. Current high-end processors can issue up to 4 or more instructions per cycle, while mainstream processors already can issue two or three instructions per cycle. Meanwhile, efforts to achieve higher clock frequencies force designers to split tasks that traditionally occupied a single pipeline stage (such as instruction decoding) into multiple stages, deepening the processor pipelines.

In these deep and wide pipelines, a continuous instruction supply is critical to sustain a high issue rate. Changes in the control flow of a program can introduce bubbles in the pipeline, resulting in underutilization of the resources, and longer execution times. Furthermore, conditional branches introduce a dependency between the execution of the branch instruction and the fetching of the target instruction. In a deep pipeline, resolving this dependency and fetching the correct target can take several cycles, during which the (multiple) resources of the processor remain idle.

Branches also introduce control dependences which restrict the ability of the compiler to rearrange instructions and achieve better instruction schedules. Control dependent computation (that is, computation who's execution depends on a branch outcome) cannot, in general, be moved across branches, unless it is safe, i.e., unless the compiler can guarantee that the computation will never cause an exception, or unless adequate hardware support is provided to buffer the exceptions until the condition is resolved (e.g., sentinel scheduling [MCH<sup>+</sup>92], or boosting [SLH90, SHL92]).

### 1.1 What can we do about branches?

A number of solutions have been proposed to deal with the limitations of branches. The general idea behind many techniques is to predict a *likely* direction for a branch and optimize the execution along that path. This general idea can used both statically during code generation, and dynamically using some information tracking mechanism.

A static manifestation of this general framework is static branch prediction, in which branches are tagged with a direction bit; this bit indicates to the processor the likely branch outcome. Static predictions can also be used by the compiler for scheduling purposes, as in the case of trace scheduling and its variants [Fis81, LFK<sup>+</sup>93, CNO<sup>+</sup>88, CMC<sup>+</sup>91]. In trace scheduling, the compiler predicts a branch and optimizes the code assuming the prediction is correct. To recover the correct state after an incorrect prediction, the compiler generates special fix-up code that will be executed when an incorrect prediction is detected. This fix-up code is responsible for reversing all the effects of the code that was incorrectly executed.

Dynamic branch prediction utilizes information collected at run time to decide which is the most likely direction for a branch. Generally, dynamic branch prediction is based on maintaining a table of counters that record the past behavior of branches [Smi81, YP92, YP93] and a selection mechanism (called a *divisor* by Young *et al.* [YGS95]) that will determine which counter to use for the prediction

of each branch. Because the direction of a branch is not by itself sufficient to allow the instruction fetch mechanism to commence fetching new instructions, a Branch Target Buffer is also used to cache branch target address [LS84]. Dynamic branch prediction techniques are significantly more accurate than static ones, and due of their simple, table-based structure, are relatively easy to implement. As a result, virtually every new processor resorts to some form of dynamic branch prediction.

Even the most accurate prediction mechanisms face performance limitations. The behavior of some branches is unpredictable, forcing a lengthy recovery action to be employed by the processor. In addition, branches restrict the ability of the compiler to schedule the code, making it harder for the execution hardware to discover the available parallelism.

One way to alleviate these limitations, is to use *if-conversion* [AKPW83] and *guarded execution* [Hsu86, HD86, Mac93, MLC<sup>+</sup>92, RYYT89, KSR94]. In guarded execution, instructions in conditional regions of code are augmented with a guard operand. This operand specifies whether the instruction should be executed or not, and the branch controlling the execution of that region can be removed from the code. As a result, the compiler or dynamic scheduler can rearrange these instructions arbitrarily, as long as the dependences are respected. Furthermore, regardless of the direction of the branch, the control flow is always sequential through the if-converted part of the code, allowing a fast, sequential instruction fetching, and eliminating the pipeline bubbles due to branches. Since the if-converted branches are not predicted, they never require corrective actions. However, these advantages come at some cost. The guarded instructions that the compiler generates may be dynamically converted into NOPs, in which case they will not contribute to the useful computation of the program. However the processor will still have to fetch and decode them, possibly preventing other useful instructions from executing.

### 1.2 Guarding Background

Guarded execution (or simply *guarding*), has been proven effective in several contexts. Originally, it was proposed by Dijkstra [Dij75] as a high level programming construct, meant to simplify the expression of algorithms and to allow the formal verification of the derived algorithms. Dijkstra allowed an arbitrary Boolean conditions to be used as the guard condition of a high level statement.

Vector processors such as the CDC STAR-100 [HT72], TI ASC [Wat72] and Cray-1 [Rus78] have long benefited from guarded execution expressed through the use of *vector masks*. A vector mask is an *N*-bit wide control register, where *N* is the number of elements in a vector register. Each bit in the vector mask controls whether the corresponding element of a destination vector register should be updated or not. Essentially the vector mask stores multiple guard conditions. Using a vector mask, loops that contain if-statements can be vectorized by breaking the loop in two phases: one in which vector instructions are used to compute the bits of the vector mask, and one in which vector instructions perform the necessary computation, with the newly computed vector mask masking the results that should not be written to their destinations. The Cray-1 also includes a scalar version of the vector mask, and a *merge* instruction which is a superset of the conditional move instruction.

Allen *et al.* formalized and generalized the idea of vector masks introducing *if-conversion* [AKPW83], a general code transformation technique that facilitates the vectorization of floating point intensive applications. As part of PFC, the Parallel Fortran Converter, if-conversion was responsible for the simplification of the control flow of loops with conditional statements by converting the control dependences introduced by branches into data dependences, which are easier for the compiler to handle. The overall operation of PFC is to convert the loops into the two phases described for use with a vector

mask: first compute the appropriate conditions, and then do the actual computation guarded with the appropriate condition. A later phase of PFC was responsible for mapping these converted loops into vector instructions using the vector masks if they were supported by the underlying architecture.

VLIW machines, for example Cydra-5 [RYYT89, DHB89], and the IBM VLIW machine [Ebc88], have also used if-conversion and guarded execution to facilitate the software pipelining of loops with conditional branches. The general methodology is to apply if-conversion to loop bodies so they become free of control dependences, and then to apply other loop scheduling technique such as software pipelining [RG91, BRRP82, Lam88, Ebc87]. These machines provided instruction set and hardware support for guarded execution. For example, the Cydra-5 contained a *predicate* field per operation, and the IBM VLIW machine supported *tree* instructions, which would evaluate an expression tree and depending on the exact conditions would nullify the appropriate operations along the branches of the tree.

Hsu and Davidson [Hsu86, HD86] used guarding on a scalar processor to allow better scheduling of decision trees. In the context of a decision tree, the conditional branches are essential because they steer the flow of control to the correct branch of the tree. These diverging control structures are not amenable to if-conversion, and guarding was used as a general purpose technique to fill multiple architectural branch delay slots. However, the only current commercial scalar instruction set to include support for guarded execution is the ARM instructions set [Mac93].

The Illinois IMPACT group [CMC<sup>+</sup>91, MCH<sup>+</sup>92, MLC<sup>+</sup>92, MHB<sup>+</sup>94, MHM<sup>+</sup>95] has developed several compilation techniques to improve the performance of guarded execution for ordinary programs. The main compilation construct they use is the *Hyperblock*, which is a compilation region that may contain ordinary, as well as guarded instructions. A hyperblock is defined to have a single entry and may have multiple exits. The IMPACT compiler performs an extensive set of code transformation techniques, such as loop restructuring, unrolling, loop peeling, etc. in order to enlarge the amount of computation that can be encapsulated in a hyperblock. The compiler chooses the most appropriate code transformation technique using profiling information.

#### 1.3 Contributions of this thesis

Why isn't guarded execution a part of many instructions set architectures? The answer is not simple; however, we can identify two key factors that hinder the general acceptance of guarding:

- It requires substantial support in the instruction set, for guard operands and new instruction specifiers. Guarding requires new opcodes and instruction formats, and perhaps additional registers or register files to hold guard conditions. While this support can be trivially added to a new instruction set, extending an existing one is considerably harder. In an existing instruction set the unused space in the instruction encoding is very limited, especially for instructions with immediate fields such as load and store instructions.

- The expected performance in an ordinary development environment is unknown. Most research

in the area of guarding has been done for numerical intensive programs, or under very controlled

environments, where plenty of information about the compiled programs is available. Under

every-day use, such a controlled environment may not be possible.

This thesis focuses on these two practical issues concerning guarded execution. Our contribution is twofold.

First, we propose a new way of supporting guarding which requires only small additions to an existing (or new) instruction set architecture (ISA). This is achieved through a new class of instructions, the GUARD instructions. GUARD instructions augment the semantics of ordinary computation to add the guard operands. GUARD instructions can also reduce the number of instructions required to perform condition evaluation and can sustain better performance than other methods for guarding.

Second, we identify a set of guarding alternatives for existing instruction sets and we evaluate their performance potential. We perform the evaluation in two steps. In the first step, we evaluate the impact of guarding on the dynamic characteristics (such as the instruction count and branch behavior) of the programs; these characteristics provide insight in the effectiveness of guarding. In the second step, we perform detailed simulations to determine the execution time for each of our guarding alternatives. The context of the evaluation is a MIPS-like processor. We carry out the evaluation assuming varying levels of support for guarding, using either the traditional specification method, or using GUARD instructions.

The thesis is organized as follows: Chapter 2 describes in detail guarded execution, its use and potential, its hardware support requirements and its ISA requirements. Chapter 3 describes the compiler support required for the effective use of guarded execution. Chapter 4 introduces GUARD instructions, a mechanism to allow the introduction of guarding in existing instruction sets, and discusses the required changes in the instruction set architecture level and at the execution hardware level. Chapter 5 presents the effect of guarding on the dynamic program characteristics. Chapter 6 presents the execution time evaluation of guarding, and Chapter 7 concludes the thesis and summarizes the implications of this work.

# Chapter 2 Guarded Execution

Guarded execution is the use of guarded instructions to express conditional program structures. In this chapter, we define the exact semantics and the key characteristics of guarded instructions, and we briefly describe *if-conversion*, a method that uses guarded instructions to express conditional computation. Then we discuss the advantages and limitations of using guarding execution and we discuss the implications of supporting guarded execution on the instruction set architecture and on the implementation of the execution engine.

#### 2.1 Semantics and use of guarded instructions

A guarded instruction is a ordinary instruction augmented with a guard condition specifier. The semantics of a guarded instruction are as follows: evaluate the guard condition and if it evaluates to true, then execute the instruction, otherwise treat the instruction as a NOP. For example, a guarded add instruction can be written as:

and its semantics would be: if goond evaluates to true, perform the addition of src1 and src2 into dst, otherwise leave dst unmodified.

The conditional nature of guarded instructions allows the expression of conditional computation structures without the use of conditional branches, since the guard operands will make sure that only the correct results are committed to the architectural state of the processor.

#### 2.1.1 Use of guarded instructions

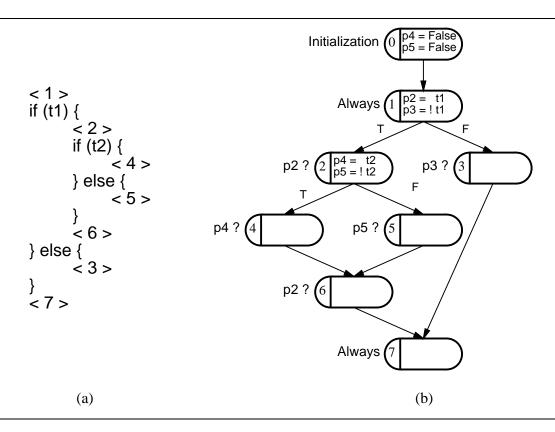

To understand why guarded execution can be a useful feature in a processor, let us first consider how a program is compiled and executed. A common program representation form used by compilers is a control flow graph (CFG). A control flow graph is a directed graph where each node is a basic block and each arc corresponds to the possible flow of control through that node. The compilation of a program can be thought of as a set of traversals of the CFG during which instructions are rearranged. During code generation, the nodes of the CFG are placed in a linear fashion in the program memory. The execution of a program can be thought of as a traversal of the linearized CFG during which the processor decides which instructions must be executed. The existence of conditional structures in the CFG gives rise to *control dependences*. A CFG node X is said to be control dependent on CFG node Y, when (i) Y has two (or more) outgoing arcs, and (ii) when the flow of control reaches node Y, node X may or may not be executed, according to the condition that selects the outgoing arc of node Y.

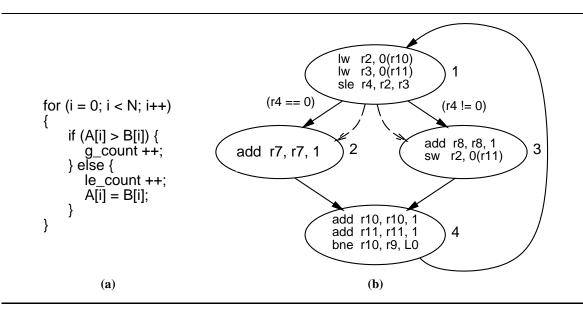

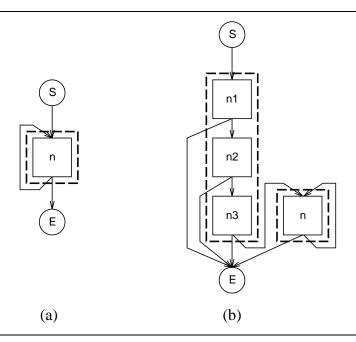

Figure 2.1 illustrates the control dependences in a CFG. Figure 2.1(a) shows the C-code for a small loop containing an if-then-else statement. Figure 2.1(b) shows the corresponding control flow graph, annotated (using dashed lines) with the control dependences. In this example node 2 and 3 are

**Figure 2.1:** A small loop and its corresponding CFG. The dashed arrows in the CFG indicated control dependences.

control dependent on node 1. Note that node 4 is not control dependent on node 1, since node 4 will be executed regardless of the outcome on the branch in node 1. Node 4 is *not* control dependent on nodes 2 and 3 since these nodes have a single exit arc.

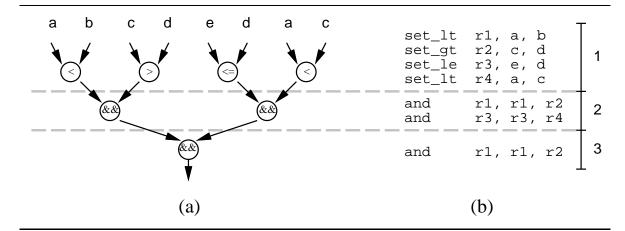

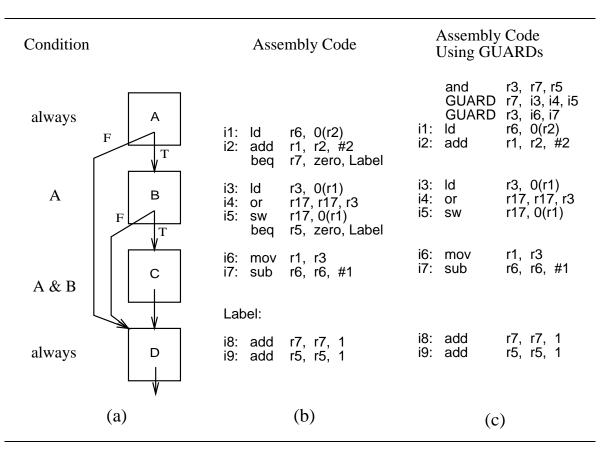

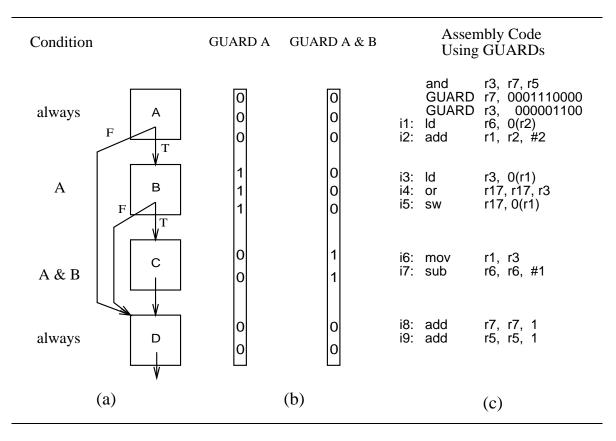

In a traditional instruction set, the conditional structures in the CFG are expressed in the assembly code using conditional branches to express the decision points (node 1) and unconditional branches to redirect the control flow to the reconvergence points (node 4) as shown in Figure 2.2(a). During the execution of the generated code, the processor navigates through the CFG by means of executing the conditional and unconditional branches.

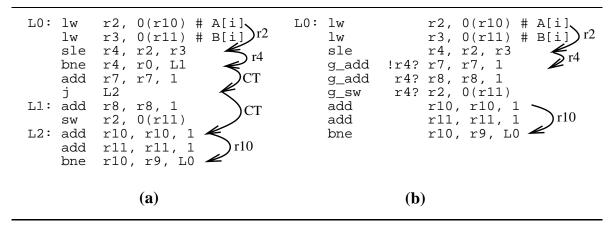

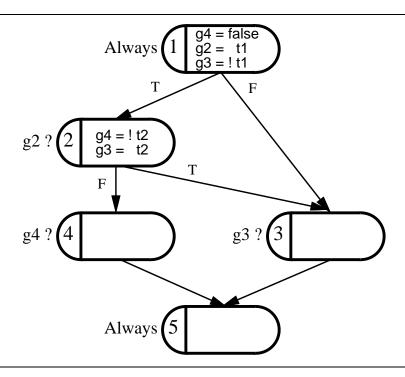

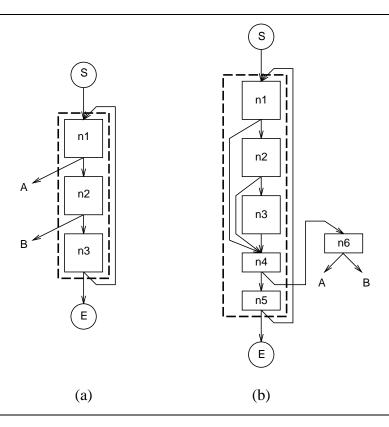

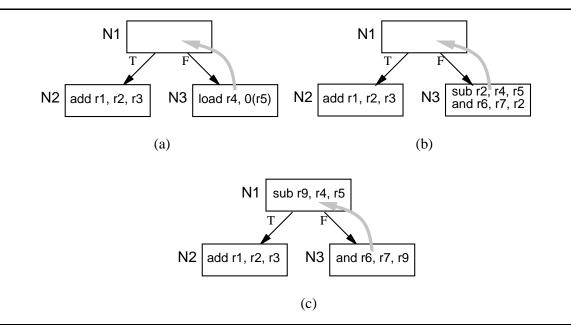

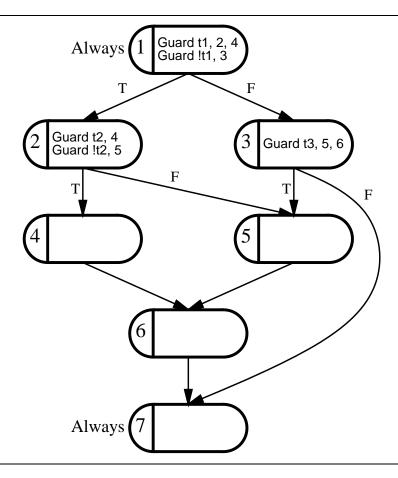

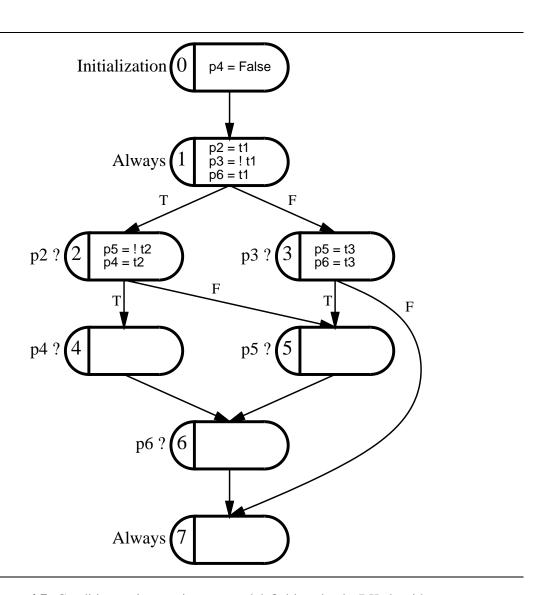

If the instruction set supports guarded instructions, a process known as *if-conversion* can be used to express the conditionally executed parts of the CFG using guarded instructions as shown in Figure 2.2(b). (In Figure 2.2(b), the prefix "g\_" denotes the guarded version of an instruction, so g\_add is a guarded add, g\_sw is a guarded store, etc; the first operand of a conditional instruction is the condition register.) If-conversion works on loop-free subsets of the CFG of a program in three steps. First, it assigns a guard condition register to each conditionally executed node. Second, it identifies where each guard condition should be set and inserts code that sets it appropriately. As a last step, if-conversion transforms all the instruction in the conditionally executed nodes into guarded instructions using the corresponding guard condition. (A detailed description of an algorithm for if-conversion will be presented in Chapter 3.) After these three steps, the control dependences are transformed into data dependences which are explicitly expressed as the settings and the uses of the guard registers.

The positive effects of guarded execution can be seen in Figure 2.2 (a) and (b). Comparing the two figures we find that two static branches were eliminated (corresponding to the if-then-else construct in the C-code), and that the basic blocks are considerably larger: the MIPS-like assembly contains eight non-branch and three branch instructions, while the guarded version contains 8 non-branch and 1 branch instructions. The instruction level parallelism is increased considerably with guarding. In Figure 2.2(a), the maximal dependence path is five or six instructions per iteration depending on

**Figure 2.2:** MIPS-like assembly for the code in Figure 2.1. Conditional computation is implemented using branches in part (a) and guarded instructions in part (b). The arrows indicate the worst dependence path(s) through the code, and are tagged with the register that causes the dependency. The CT tag stands for "Control Transfer".

whether the conditional branch is taken or not. (The arrows in the right of the assembly code indicate the worst path corresponding to the not-taken case.) In Figure 2.2(b), the maximal dependence is three instructions per iteration. Assuming adequate resources, data cache hits and equal probability for each direction of the conditional branch, the execution the non-guarded version of the code will take 6.5 cycles on the average (the two possible paths are 5 and 6 instructions long plus one cycle for the load latency), while the execution of the guarded version of the code will take 4 cycles (a critical path of three instructions plus one cycle for the load latency), corresponding to a 62% speedup.

#### 2.1.2 Advantages of guarding

The previous example illustrated that a seemingly small difference, the conversion of control dependences into data dependences, had a significant impact on the execution time of the code. The reason is that control dependences have a negative effect both on the compiler and on the processor which was relieved by the conversion.

When if-conversion is used, several basic blocks of the CFG are merged together. The combined basic block contains more instructions and presents more scheduling opportunities and flexibility. A compiler for an instruction level parallel processor generally has to first identify the set of instructions that are independent, and then schedule them so they are executed in parallel. Under realistic assumptions, the processor resources are finite and the compiler has the additional task of scheduling resource usage among the competing instructions. The larger basic blocks after if-conversion generally contain larger amounts of parallelism, permitting the compiler to produce instructions schedules that are more parallel and match the processor resources better.

Furthermore, after if-conversion, instructions from different control paths can be freely intermixed, allowing instruction schedules that overlap different control paths during execution, a flexibility that is shown to have significant performance potential; Lam and Wilson [LW92] found that allowing the execution of multiple flows of control almost tripled the amount of parallelism exposed to their

abstract machine models. In essence, the ability to overlap different control paths is similar to *global scheduling* techniques [Nic85, Smi92]. The removal of control dependences also can increase the effectiveness of other code transformation techniques such as software pipelining [RG91, BRRP82, Lam88, Ebc87], modulo scheduling [Rau94], etc.

For the instruction fetch unit of a processor, the larger, if-converted basic blocks allow for higher instruction fetch efficiency. Small basic blocks cause frequent changes in the flow of control, resulting in under-utilization of the instruction fetch bandwidth and the processor resources. The execution of if-converted straight-line code benefits from an instruction memory system that provides high bandwidth, but not necessarily short latency. High bandwidth from the instruction memory to the processor, is relatively cheap for single chip implementations, since the processor can take advantage of a wide on-chip instruction cache. Furthermore, prefetching can be used to shorten the latency due to instruction cache misses during sequential parts of instruction fetch.

Processors employing dynamic branch prediction, can also benefit from guarding. For programs with small basic blocks, multiple predictions per cycle may be required to find enough instructions and to fully utilize the pipeline resources [YMP93]. The larger basic blocks of the if-converted code keep the pipeline more full, reducing the importance of multiple predictions per cycle. A smaller number of predictions usually generates fewer mispredictions. For every misprediction, the processor has to invoke a recovery action to undo the effects of the mis-speculated instructions and commence the instruction fetching from the correct target. Since these recovery actions can cost several cycles, reducing the number of mispredictions will reduce the total execution time of programs. The advantages of guarding are summarized in the top part of Table 2.1.

#### 2.1.3 Limitations of guarding

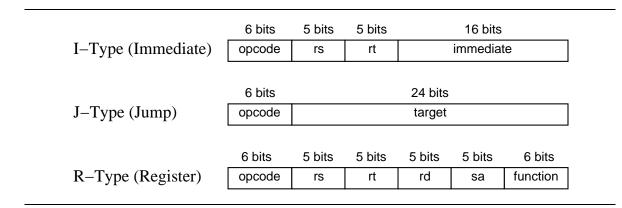

However guarded execution is not without limitations. First, guarded execution requires adequate support in the Instruction Set Architecture (ISA) level. This support that may range from a few new instructions, to a complete overhaul of the architecture and the instruction set. Providing adequate ISA support for guarding may be relatively easy when designing a new architecture, but extending an existing architecture is a much more challenging endeavor. Section 2.2 of this chapter will discuss in detail the instruction set requirements of guarding.

A second limitation of guarding is that it increases the total number of instructions executed dynamically. In general, instructions from both paths (traversed and not traversed) of a branch instruction are transformed into guarded instructions; the processor has to fetch and decode all these instructions, since it has no prior knowledge of which instructions will be useful until the instructions are fetched and examined, and the corresponding conditions (if any) are evaluated. After the condition evaluation, instructions from the not-traversed path are transformed into NOPs in the earlier stages of the pipeline (these NOPs need not be executed, but they will consume part of the fetch and decode bandwidth of the processor). These extra instructions, from the not-traversed path, may be scheduled to execute in parallel with other useful computation, if the processor has a sufficient number of resources. If sufficient resources do not exist, the additional instructions can actually increase the overall execution time. The execution time may also increase if the paths are of unequal lengths: when the longer path cannot be scheduled in parallel with other useful computation, the shorter path might have to be lengthened and performance along that path will suffer.

A third limitation of guarding is that the addition of guard operand(s) to each guarded instruction requires additional read port(s) in the register file. The additional read ports are used to read the

|             | Fewer control dependencies allow better compiler schedules                  |

|-------------|-----------------------------------------------------------------------------|

|             | Larger Basic Blocks present more parallelism to compiler                    |

|             | Compiler can overlap execution of different control paths                   |

| Adventeges  | Improves or facilitates other compiler optimizations (S/W pipelining, etc.) |

| Advantages  | Large sequential blocks of instructions                                     |

|             | Fewer control flow changes                                                  |

|             | Less important to predict multiple branches per cycle                       |

|             | Fewer mispredictions and fewer recovery actions                             |

|             | Requires ISA support                                                        |

|             | Increases the dynamic instruction count                                     |

| Limitations | Requires additional read port(s) in the register file                       |

|             | Consumes architecturally visible registers                                  |

|             | Requires adequate compiler support                                          |

**Table 2.1:** Advantages and limitations of guarding.

guard operand(s) of a guarded instructions in parallel with its regular source operands. The additional read ports will increase the size of the register file and can make it slower.

Finally, the conversion of control dependences to data dependences consumes architecturally visible registers. Without guarding, the register that holds the condition is used once to decide the branch outcome and set the correct PC value. With guarding, the condition register is used as a source operand in all the instructions it covers. Therefore, the lifetime of this register must extend to the last guarded instruction, thus increasing the register pressure. The problem is exacerbated by the instruction scheduler which, by rearranging instructions to increase parallelism, can increase the register lifetimes. One possible solution to this problem is to add a separate predicate register file [MLC<sup>+</sup>92, RYYT89, KSR94], to relieve the pressure on the general purpose registers. This solution, however, is a major architectural change and may not be easily incorporated into existing architectures. Table 2.1 summarizes the advantages and limitations of guarding.

## 2.2 Instruction set support for guarding